# **SUNRISE Technology**

## **SPECIFICATION**

| SPEC. NO. : | ·       | <b>REV</b> :                             |

|-------------|---------|------------------------------------------|

| DATE:       | _2021.0 | 07.22                                    |

| PRODUCT     | NAME:   | Al00240  Bluetooth Low Energy 5.0 Module |

|      | APPROVED | CHECKED | PREPARED | DCC ISSUE |

|------|----------|---------|----------|-----------|

| NAME |          |         |          |           |

## **INDEX**

| Key Features                                                   | 1   |

|----------------------------------------------------------------|-----|

| Applications                                                   | 2   |

| 1. Interface Description                                       | 3   |

| 1-1. PIN Diagram                                               |     |

| 1-2. PIN Description                                           |     |

| 1-3. MCU(nRF52832) Block Diagram                               | . 6 |

| 1-4. Module Block Diagram                                      | . 7 |

| 2 · Electrical Specification                                   | 8   |

| 2-1. Absolute maximum ratings                                  | . 8 |

| 2-2. Operation Condition                                       | . 8 |

| 2-3. General Radio Characteristics                             | . 8 |

| 2-4. Radio Current Consumption (Transmitter)                   | . 9 |

| 2-5. Radio current consumption (Receiver)                      |     |

| 2-6. Transmitter specification                                 |     |

| 2-7. Receiver operation                                        |     |

| 2-8. RX selectivity                                            |     |

| 2-9. RX intermodulation                                        |     |

| 2-10. Radio timing                                             |     |

| 2-11. Received Signal Strength Indicator (RSSI) specifications |     |

| 2-12. Jitter                                                   |     |

| 2-13. Delay when disabling the RADIO                           |     |

| 2-14. CPU performance                                          |     |

| 3 · GPIO — General purpose input/output                        |     |

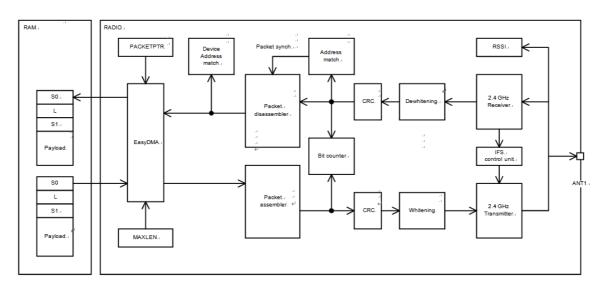

| 4 · RADIO — 2.4 GHz Radio                                      | 18  |

| 5 · SPI — Serial peripheral interface master                   | 19  |

| 6 · TWI — I <sup>2</sup> C compatible two-wire interface       | 21  |

| 7 · UART — Universal asynchronous receiver/ transmitter        |     |

| 8 × PCB Printed Antenna Information                            |     |

| APPENDIX A: CERTIFICATION NOTICES                              |     |

| APPENDIX B: LABEL FOR FINISHED PRODUCT                         |     |

|                                                                |     |

| Version Information                                            | 30  |

| ZZ DLANIZ SS                                                   | 24  |

## **Bluetooth Low Energy 5.0 Module**

### **Key Features**

- ➤ Bluetooth 5, 2 Mbps, CSA #2, Advertising Extensions

- ➤ 64 MHz ARM® Cortex-M4F processor

- 512 KB Flash + 64 KB RAM

- Software stacks available as downloads

- Supports 1 Mbps and 2 Mbps Bluetooth LE modes

- ➤ 100 dB link budget

- Sensitivity of -96 dbm for Bluetooth LE

- Programmable output power +4 dBm to -20 dBm

- > RSSI with 1 dB resolution

- Flexible and configurable 32 pin GPIO

- Programmable Peripheral Interface PPI

- Automatic smart power management

- ➤ Full set of digital interfaces including: SPI/2-wire/I²S/UART/PDM/QDEC with EasyDMA

- > 12-bit/200 ksps ADC

- ➤ 128-bit AES ECB/CCM/AAR co-processor

- $\triangleright$  Integrated balun with 50 Ω single-ended output

- ➤ Ultra low-power 32 kHz crystal and RC oscillators

- ➤ Wide supply voltage range (1.7 V to 3.6 V)

- On-chip DC/DC buck converter

- Individual power management for all peripherals

- 2 channels 4 levels Low Voltage Detector

#### **Power Supply**

VDD input is 1.7V to 3.6V

#### Antenna

Printed Antenna

#### **Temperature**

➤ Operating temperature: -40°C to +85°C

Storage temperature: -65°C to +150°C

## **Applications**

- ▶ IoT

- ♦ Home automation

- ♦ Sensor networks

- ♦ Building automation

- Personal Area Networks

- ♦ Health / fitness sensor and monitor device

- ♦ Medical devices

- ♦ Key-fobs and wrist watches

- Interactive entertainment devices

- ♦ Remote control

- ♦ Gaming controller

- Beacons

- > A4WP wireless chargers and devices

- Remote control toys

- Computer peripherals and I/O devices

- ♦ Mouse

- ♦ Keyboard

- ♦ Multi-touch trackpad

## 1. Interface Description

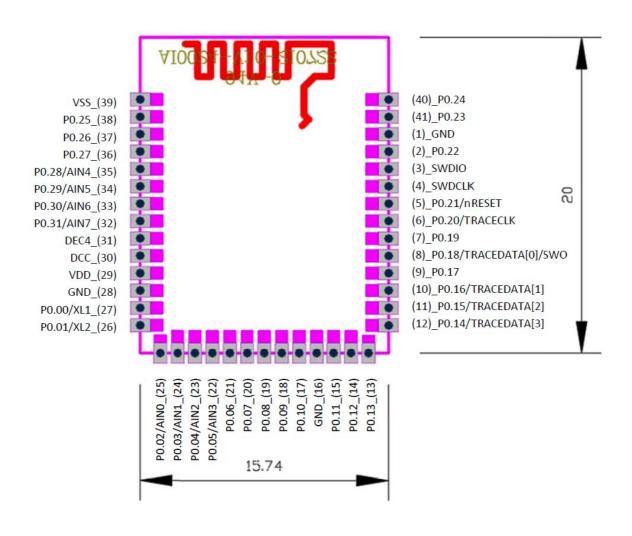

### 1-1. PIN Diagram

Figure 1-1 Al00240 PIN Diagram

## 1-2. PIN Description

Table1-3

| PIN<br>NO. | Name   | I/O<br>Type | Function Description                                    | Other Function                            |

|------------|--------|-------------|---------------------------------------------------------|-------------------------------------------|

| 1          | GND    | G           | The pad must be connected to a solid ground plane       |                                           |

| 2          | P0.22  | I/O         | General-purpose digital I/O                             |                                           |

| 3          | SWDIO  | I/O         | Serial Wire debug I/O for debug and programming         |                                           |

| 4          | SWDCLK | I           | Serial Wire debug clock input for debug and programming |                                           |

| 5          | P0.21  | I/O         | General-purpose digital I/O                             | RESET<br>Configurable as system RESET pin |

| 6          | P0.20  | I/O         | General-purpose digital I/O                             | TraceCLK<br>Trace port clock output       |

| 7          | P0.19  | I/O         | General-purpose digital I/O                             |                                           |

| 8          | P0.18  | I/O         | General-purpose digital I/O                             |                                           |

| 9          | P0.17  | I/O         | General-purpose digital I/O                             | TraceData(0)<br>Trace port output         |

| 10         | P0.16  | I/O         | General-purpose digital I/O                             | TraceData(2)<br>Trace port output         |

| 11         | P0.15  | I/O         | General-purpose digital I/O                             | TraceData(1)<br>Trace port output         |

| 12         | P0.14  | I/O         | General-purpose digital I/O                             | TraceData(3)<br>Trace port output         |

| 13         | P0.13  | I/O         | General-purpose digital I/O                             |                                           |

| 14         | P0.12  | I/O         | General-purpose digital I/O                             |                                           |

| 15         | P0.11  | I/O         | General-purpose digital I/O                             |                                           |

| 16         | GND    | G           | General-purpose digital I/O                             |                                           |

| 17         | P0.10  | I/O         | General-purpose digital I/O                             |                                           |

| 18         | P0.09  | I/O         | General-purpose digital I/O                             |                                           |

| 19         | P0.08  | I/O         | General-purpose digital I/O                             |                                           |

| 20 | P0.07 | I/O | General-purpose digital I/O                                                       |                                                               |

|----|-------|-----|-----------------------------------------------------------------------------------|---------------------------------------------------------------|

| 21 | P0.06 | I/O | General-purpose digital I/O                                                       |                                                               |

| 22 | P0.05 | I/O | General-purpose digital I/O                                                       | AIN3_Analog input<br>SAADC/COMP/LPCOMPinput                   |

| 23 | P0.04 | I/O | General-purpose digital I/O                                                       | AIN2_Analog input<br>SAADC/COMP/LPCOMPinput                   |

| 24 | P0.03 | I/O | General-purpose digital I/O                                                       | AIN1_Analog input<br>SAADC/COMP/LPCOMPinput                   |

| 25 | P0.02 | I/O | General-purpose digital I/O                                                       | AIN0_Analog input<br>SAADC/COMP/LPCOMPinput                   |

| 26 | P0.01 | I/O | General-purpose digital I/O                                                       | XL2_Analog input<br>Connection to 32.768khz crystal<br>(LFXO) |

| 27 | P0.00 | I/O | General-purpose digital I/O                                                       | XL1_Analog input<br>Connection to 32.768khz crystal<br>(LFXO) |

| 28 | GND   | G   | The pad must be connected to a solid ground plane                                 |                                                               |

| 29 | vcc   | Р   | Power-supply pin                                                                  |                                                               |

| 30 | DCC   | Р   | DC/DC converter output pin                                                        |                                                               |

| 31 | DEC4  | Р   | 1V3 regulator supply decoupling. Input from DC/DC converter. Output from 1V3 LDO. |                                                               |

| 32 | P0.31 | I/O | General-purpose digital I/O                                                       | AIN7_ Analog input<br>SAADC/COMP/LPCOMPinput                  |

| 33 | P0.30 | I/O | General-purpose digital I/O                                                       | AIN6_ Analog input<br>SAADC/COMP/LPCOMPinput                  |

| 34 | P0.29 | I/O | General-purpose digital I/O                                                       | AIN5_ Analog input<br>General-purpose digital I/O             |

| 35 | P0.28 | I/O | General-purpose digital I/O                                                       | AIN4_ Analog input<br>SAADC/COMP/LPCOMPinput                  |

| 36 | P0.27 | I/O | General-purpose digital I/O                                                       |                                                               |

| 37 | P0.26 | I/O | General-purpose digital I/O                                                       |                                                               |

| 38 | P0.25 | I/O | General-purpose digital I/O                                                       |                                                               |

| 39 | GND   | G   | The pad must be connected to a solid ground plane                                 |                                                               |

| 40 | P0.24 | I/O | General-purpose digital I/O                                                       |                                                               |

| 41 | P0.23 | I/O | General-purpose digital I/O                                                       |                                                               |

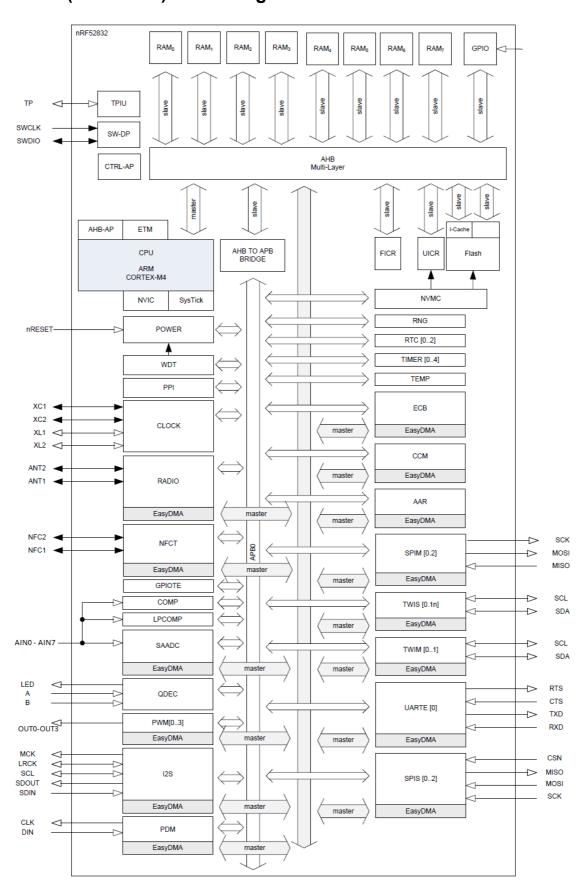

### 1-3. MCU(nRF52832) Block Diagram

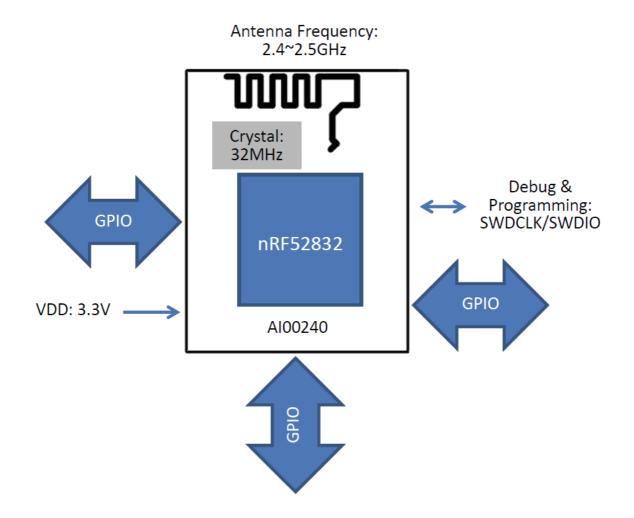

### 1-4. Module Block Diagram

## 2. Electrical Specification

Any technical spec shall refer to Nordic's official documents as final reference. Contents below are from "nRF52832 Product Specification v1.4", please click to download full spec.

#### 2-1. Absolute maximum ratings

|                                     | Min.             | Max.        | Unit               |

|-------------------------------------|------------------|-------------|--------------------|

| <b>Supply voltages</b>              |                  |             |                    |

| VDD                                 | -0.3             | +3.9        | V                  |

| VSS                                 |                  | 0           | V                  |

| I/O pin voltage                     |                  |             |                    |

| VI/O, VDD ≤3.6 V                    | -0.3             | VDD + 0.3 V | V                  |

| Environmental QFN48, 6×6 mm package |                  |             |                    |

| Storage temperature                 | -40              | +125        | °C                 |

| MSL (moisture sensitivity level)    |                  | 2           |                    |

| ESD HBM (human body model)          |                  | 4           | kV                 |

| ESD CDM (charged device model)      |                  | 1000        | V                  |

| Flash memory                        |                  |             |                    |

| Endurance                           | 10 000           |             | Write/erase cycles |

| Retention                           | 10 years at 40°C |             |                    |

### 2-2. Operation Condition

| Symbol | Parameter                                  | Notes | Min. | Nom. | Max. | Units |

|--------|--------------------------------------------|-------|------|------|------|-------|

| VDD    | Supply voltage, independent of DCDC enable |       | 1.7  | 3.0  | 3.6  | V     |

| tR_VDD | Supply rise time (0 V to 1.7 V)            |       |      |      | 60   | ms    |

| TA     | Operating temperature                      |       | -40  | 25   | 85   | °C    |

**Important:** The on-chip power-on reset circuitry may not function properly for rise times longer than the specified maximum.

#### 2-3. General Radio Characteristics

| Symbol        | Description                      | Min. | Тур. | Max. | Units |

|---------------|----------------------------------|------|------|------|-------|

| fOP           | Operating frequencies            | 2360 |      | 2500 | MHz   |

| fPLL,PROG,RES | PLL programming resolution       |      | 2    |      | kHz   |

| fPLL,CH,SP    | PLL channel spacing              |      | 1    |      | MHz   |

| fDELTA,1M     | Frequency deviation @ 1 Msps     |      | ±170 |      | kHz   |

| fDELTA,BLE,1M | Frequency deviation @ BLE 1Msps  |      | ±250 |      | kHz   |

| fDELTA,2M     | Frequency deviation @ 2 Msps     |      | ±320 |      | kHz   |

| fDELTA,BLE,2M | Frequency deviation @ BLE 2 Msps |      | ±500 |      | kHz   |

| fskSPS        | On-the-air data rate             | 1    |      | 2    | Msps  |

2-4. Radio Current Consumption (Transmitter)

| Symbol              | Description                                | Min. | Тур. | Max. | Units |

|---------------------|--------------------------------------------|------|------|------|-------|

| ITX,PLUS4Dbm,DCDC   | TX only run current (DCDC, 3V) PRF =+4 dBm |      | 7.5  |      | mA    |

| ITX,PLUS4Dbm        | TX only run current PRF = +4 dBm           |      | 16.6 |      | mA    |

| ITX,0Dbm,DCDC       | TX only run current (DCDC, 3V)PRF = 0dBm   |      | 5.3  |      | mA    |

| ITX,0Dbm            | TX only run current PRF = 0dBm             |      | 11.6 |      | mA    |

| lTX,MINUS4Dbm,DCDC  | TX only run current DCDC, 3V PRF = -4dBm   |      | 4.2  |      | mA    |

| ITX,MINUS4Dbm       | TX only run current PRF = -4 dBm           |      | 9.3  |      | mA    |

| ITX,MINUS8Dbm,DCDC  | TX only run current DCDC, 3V PRF = -8 dBm  |      | 3.8  |      | mA    |

| ITX,MINUS8Dbm       | TX only run current PRF = -8 dBm           |      | 8.4  |      | mA    |

| ITX,MINUS12Dbm,DCDC | TX only run current DCDC, 3V PRF = -12 dBm |      | 3.5  |      | mA    |

| ITX,MINUS12Dbm      | TX only run current PRF = -12 dBm          |      | 7.7  |      | mA    |

| ITX,MINUS16Dbm,DCDC | TX only run current DCDC, 3V PRF = -16 dBm |      | 3.3  |      | mA    |

| ITX,MINUS16Dbm      | TX only run current PRF = -16 dBm          |      | 7.3  |      | mA    |

| ITX,MINUS20Dbm,DCDC | TX only run current DCDC, 3V PRF = -20 dBm |      | 3.2  |      | mA    |

| ITX,MINUS20Dbm      | TX only run current PRF = -20 dBm          |      | 7.0  |      | mA    |

| ITX,MINUS40Dbm,DCDC | TX only run current DCDC, 3V PRF = -40 dBm |      | 2.7  |      | mA    |

| ITX,MINUS40Dbm      | TX only run current PRF = -40 dBm          |      | 5.9  |      | mA    |

| ISTART,TX,DCDC      | TX start-up current DCDC, 3V, PRF = 4 dBm  |      | 4.0  |      | mA    |

| ISTART,TX           | TX start-up current, PRF = 4 dBm           |      | 8.8  |      | mA    |

2-5. Radio current consumption (Receiver)

| Symbol         | Description                                      | Min. | Тур. | Max. | Units |

|----------------|--------------------------------------------------|------|------|------|-------|

| IRX,1M,DCDC    | RX only run current (DCDC, 3V) 1Msps / 1Msps BLE |      | 5.4  |      | mA    |

| IRX,1M         | RX only run current 1Msps / 1Msps BLE            |      | 11.7 |      | mA    |

| IRX,2M,DCDC    | RX only run current (DCDC, 3V) 2Msps / 2Msps BLE |      | 5.8  |      | mA    |

| IRX,2M         | RX only run current 2Msps / 2Msps BLE            |      | 12.9 |      | mA    |

| ISTART,RX,DCDC | RX start-up current (DCDC 3V)                    |      | 3.5  |      | mA    |

| ISTART,RX,LDO  | RX start-up current (LDO 3V)                     |      | 7.5  |      | mA    |

2-6. Transmitter specification

| Symbol | Description                                                                               | Min. | Тур. | Max. | Units |

|--------|-------------------------------------------------------------------------------------------|------|------|------|-------|

| PRF    | Maximum output power                                                                      |      | 4    | 6    | dBm   |

| PRFC   | RF power control range                                                                    |      | 24   |      | dB    |

| PRFCR  | RF power accuracy                                                                         |      |      | ±4   | dB    |

| PRF1,1 | 1 <sup>st</sup> Adjacent Channel Transmit Power 1 MHz (1<br>Msps Nordic proprietary mode) |      | -25  |      | dBc   |

| PRF2,1 | 2 <sup>nd</sup> Adjacent Channel Transmit Power 2 MHz (1 Msps<br>Nordic proprietary mode) |      | -50  |      | dBc   |

| PRF1,2     | 1 <sup>st</sup> Adjacent Channel Transmit Power 2 MHz (2<br>Msps Nordic proprietary mode) | -25 | dBc |

|------------|-------------------------------------------------------------------------------------------|-----|-----|

| PRF2,2     | 2 <sup>nd</sup> Adjacent Channel Transmit Power 4 MHz (2 Msps<br>Nordic proprietary mode) | -50 | dBc |

| PRF1,2,BLE | 1 <sup>st</sup> Adjacent Channel Transmit Power 2 MHz (2 Msps<br>BLE mode)                | -20 | dBc |

| PRF2,2,BLE | 2 <sup>nd</sup> Adjacent Channel Transmit Power 4 MHz (2<br>Msps BLE mode)                | -50 | dBc |

### 2-7. Receiver operation

| Symbol             | Description                                                                         | Min. | Тур. | Max. | Units |

|--------------------|-------------------------------------------------------------------------------------|------|------|------|-------|

| PRX,MAX            | Maximum received signal strength at < 0.1% BER                                      |      | 0    |      | dBm   |

| PSENS,IT,1M        | Sensitivity, 1Msps nRF mode <sup>1</sup>                                            |      | -93  |      | dBm   |

| PSENS,IT,SP,1M,BLE | Sensitivity, 1Msps BLE ideal transmitter, $\stackrel{<}{-}$ 37 bytes BER=1E- $^3$ 2 |      | -96  |      | dBm   |

| PSENS,IT,LP,1M,BLE | Sensitivity, 1Msps BLE ideal transmitter >=128 bytes BER=1E-43 <sup>3</sup>         |      | -95  |      | dBm   |

| PSENS,IT,2M        | Sensitivity, 2Msps nRF mode <sup>4</sup>                                            |      | -89  |      | dBm   |

Typical sensitivity applies when ADDR0 is used for receiver address correlation. When ADDR[1...7] are used for receiver address correlation, the typical sensitivity for this mode is degraded by 3dB.

As defined in the Bluetooth Core Specification v4.0 Volume 6: Core System Package (Low Energy Controller Volume)

<sup>3</sup> Equivalent BER limit < 10E-04

<sup>&</sup>lt;sup>4</sup> Typical sensitivity applies when ADDR0 is used for receiver address correlation. When ADDR[1...7] are used for receiver address correlation, the typical sensitivity for this mode is degraded by 3dB.

| Symbol                | Description                                                         | Min. | Тур. | Max. | Units |

|-----------------------|---------------------------------------------------------------------|------|------|------|-------|

| PSENS,IT,SP,2M,BLE    | Sensitivity, 2Msps BLE ideal transmitter, Packet length             |      | -93  |      | dBm   |

|                       | <=37bytes                                                           |      |      |      |       |

| PSENS,DT,SP,2M,BLE    | Sensitivity, 2Msps BLE dirty transmitter, Packet length             |      | -93  |      | dBm   |

| · SENS,D1,SF,ZIVI,DEL | <=37bytes                                                           |      | -93  |      | ubili |

| PSENS,IT,LP,2M,BLE    | Sensitivity, 2Msps BLE ideal transmitter >= 128bytes                |      | -92  |      | dBm   |

| PSENS,DT,LP,2M,BLE    | Sensitivity, 2Msps BLE dirty transmitter, Packet length >= 128bytes |      | -92  |      | dBm   |

### 2-8. RX selectivity

RX selectivity with equal modulation on interfering signal 1

| Symbol                   | Description                                 | Min. | Тур. | Max. | Units |

|--------------------------|---------------------------------------------|------|------|------|-------|

| C/I1M,co-channel         | 1Msps mode, Co-Channel interference         |      | 9    |      | dB    |

| C/I <sub>1M</sub> ,-1MHz | 1 Msps mode, Adjacent (-1 MHz) interference |      | -2   |      | dB    |

| C/I <sub>1M</sub> ,+1MHz | 1 Msps mode, Adjacent (+1 MHz) interference |      | -10  |      | dB    |

| C/I1M,-2MHz              | 1 Msps mode, Adjacent (-2 MHz) interference |      | -19  |      | dB    |

| C/I <sub>1M</sub> ,+2MHz | 1 Msps mode, Adjacent (+2 MHz) interference |      | -42  |      | dB    |

| C/I <sub>1M</sub> ,-3MHz | 1 Msps mode, Adjacent (-3 MHz) interference |      | -38  |      | dB    |

| C/I1M,+3MHz              | 1 Msps mode, Adjacent (+3 MHz) interference |      | -48  |      | dB    |

| C/I1M,±6MHz              | 1 Msps mode, Adjacent (≥6 MHz) interference |      | -50  |      | dB    |

| C/I1MBLE,co-channel      | 1 Msps BLE mode, Co-Channel interference    |      | 6    |      | dB    |

### A100240

| C/I1MBLE,-1MHz      | 1 Msps BLE mode, Adjacent (-1 MHz) interference          | -2  | dB |

|---------------------|----------------------------------------------------------|-----|----|

| C/I1MBLE,+1MHz      | 1 Msps BLE mode, Adjacent (+1 MHz) interference          | -9  | dB |

| C/I1MBLE,-2MHz      | 1 Msps BLE mode, Adjacent (-2 MHz) interference          | -22 | dB |

| C/I1MBLE,+2MHz      | 1 Msps BLE mode, Adjacent (+2 MHz) interference          | -46 | dB |

| C/I1MBLE,>3MHz      | 1 Msps BLE mode, Adjacent (≥3 MHz) interference          | -50 | dB |

| C/I1MBLE,image      | Image frequency Interference                             | -22 | dB |

| C/I1MBLE,image,1M   | Adjacent (1 MHz) interference to in-band image frequency | -35 | dB |

| C/I2M,co-channel    | 2Msps mode, Co-Channel interference                      | 10  | dB |

| C/I2M,-2MHz         | 2 Msps mode, Adjacent (-2 MHz) interference              | 6   | dB |

| C/I2M,+2MHz         | 2 Msps mode, Adjacent (+2 MHz) interference              | -14 | dB |

| C/I2M,-4MHz         | 2 Msps mode, Adjacent (-4 MHz) interference              | -20 | dB |

| C/I2M,+4MHz         | 2 Msps mode, Adjacent (+4 MHz) interference              | -44 | dB |

| C/I2M,-6MHz         | 2 Msps mode, Adjacent (-6 MHz) interference              | -42 | dB |

| C/I2M,+6MHz         | 2 Msps mode, Adjacent (+6 MHz) interference              | -47 | dB |

| C/I2M,≥12MHz        | 2 Msps mode, Adjacent (≥12 MHz) interference             | -52 | dB |

| C/I2MBLE,co-channel | 2 Msps BLE mode, Co-Channel interference                 | 7   | dB |

| C/I2MBLE,±2MHz      | 2 Msps BLE mode, Adjacent (±2 MHz) interference          | 0   | dB |

| C/I2MBLE,±4MHz      | 2 Msps BLE mode, Adjacent (±4 MHz) interference          | -47 | dB |

| C/I2MBLE,≥6MHz      | 2 Msps BLE mode, Adjacent (≥6 MHz) interference          | -49 | dB |

| C/I2MBLE,image      | Image frequency Interference                             | -21 | dB |

| C/I2MBLE,image,     | Adjacent (2 MHz) interference to in-band image frequency | -36 | dB |

|                     |                                                          |     |    |

Wanted signal level at PIN = -67 dBm. One interferer is used, having equal modulation as the wanted signal. The input power of the interferer where the sensitivity equals BER = 0.1% is presented

### 2-9. RX intermodulation

RX intermodulation<sup>1</sup>

| Symbol      | Description                                                  | Min. | Тур. | Max. | Units |

|-------------|--------------------------------------------------------------|------|------|------|-------|

| PIMD,1M     | IMD performance, 1 Msps (3 MHz, 4 MHz, and 5 MHz offset)     |      | -33  |      | dBm   |

| PIMD,1M,BLE | IMD performance, BLE 1 Msps (3 MHz, 4 MHz, and 5 MHz offset) |      | -30  |      | dBm   |

| PIMD,2M     | IMD performance, 2 Msps (6 MHz, 8 MHz, and 10 MHz offset)    |      | -33  |      | dBm   |

Wanted signal level at PIN = -64 dBm. Two interferers with equal input power are used. The interferer closest in frequency is not modulated, the other interferer is modulated equal with the wanted signal. The input power of the interferers where the sensitivity equals BER = 0.1% is presented.

| Symbol      | Description                                                   | Min. | Тур. | Max. | Units |

|-------------|---------------------------------------------------------------|------|------|------|-------|

| PIMD,2M,BLE | IMD performance, BLE 2 Msps (6 MHz, 8 MHz, and 10 MHz offset) |      | -32  |      | dBm   |

### 2-10. Radio timing

| Symbol           | Description          |                |               | Min.    | Тур.       | Max.    | Units |

|------------------|----------------------|----------------|---------------|---------|------------|---------|-------|

| ttxen            | Time between TXEN ta | sk and READY e | vent after    |         | 140        |         | us    |

| SUNRISE Technolo | ogy Co., Ltd.        | 11             | Proprietary & | Confide | ntial Info | ormatio | n     |

|               | channel FREQUENCY configured                                                                   |     |    |

|---------------|------------------------------------------------------------------------------------------------|-----|----|

| ttxen,fast    | Time between TXEN task and READY event after channel FREQUENCY configured (Fast Mode)          | 40  | us |

| tTXDISABLE    | Time between DISABLE task and DISABLED event when the radio was in TX and mode is set to 1Msps | 6   | us |

| tTXDISABLE,2M | Time between DISABLE task and DISABLED event when the radio was in TX and mode is set to 2Msps | 4   | us |

| tRXEN         | Time between the RXEN task and READY event after channel FREQUENCY configured in default mode  | 140 | us |

| trxen,fast    | Time between the RXEN task and READY event after channel FREQUENCY configured in fast mode     | 40  | us |

| tSWITCH       | The minimum time taken to switch from RX to TX or TX to RX (channel FREQUENCY unchanged)       | 20  | us |

| tRXDISABLE    | Time between DISABLE task and DISABLED event when the radio was in RX                          | 0   | us |

| ttxchain      | TX chain delay                                                                                 | 0.6 | us |

| trxchain      | RX chain delay                                                                                 | 9.4 | us |

| tRXCHAIN,2M   | RX chain delay in 2Msps mode                                                                   | 5   | us |

### 2-11. Received Signal Strength Indicator (RSSI) specifications

| Symbol         | Description                              | Min. | Тур. | Max. | Units |

|----------------|------------------------------------------|------|------|------|-------|

| RSSIACC        | RSSI Accuracy Valid range -90 to -20 dBm |      | ±2   |      | dB    |

| RSSIRESOLUTION | RSSI resolution                          |      | 1    |      | dB    |

| RSSIPERIOD     | Sample period                            |      | 0.25 |      | us    |

### 2-12. Jitter

| Symbol          | Description                                                                                      | Min. | Тур. | Max. | Units |

|-----------------|--------------------------------------------------------------------------------------------------|------|------|------|-------|

| tDISABLEDJITTER | Jitter on DISABLED event relative to END event when shortcut between END and DISABLE is enabled. |      | 0.25 |      | us    |

| treadyjitter    | Jitter on READY event relative to TXEN and RXEN task.                                            |      | 0.25 |      | us    |

## 2-13. Delay when disabling the RADIO

| Symbol        | Description                                                                  | Min. | Тур. | Max. | Units |

|---------------|------------------------------------------------------------------------------|------|------|------|-------|

| tTXDISABLE,1M | Disable delay from TX.                                                       |      | 6    |      | us    |

|               | Delay between DISABLE and DISABLED for MODE = Nrf_1Mbit and MODE = Ble_1Mbit |      |      |      |       |

| tRXDISABLE,1M | Disable delay from RX.                                                       |      | 0    |      | us    |

|               | Delay between DISABLE and DISABLED for MODE = Nrf_1Mbit and MODE = Ble_1Mbit |      |      |      |       |

### 2-14. CPU performance

The CPU clock speed is 64 MHz. Current and efficiency data is taken when in System ON and the CPU is executing the CoreMark<sup>™</sup> benchmark. It includes power regulator and clock base currents. All other blocks are IDLE.

| Symbol                | Description                                                 | Min. | Тур. | Max. | Units       |

|-----------------------|-------------------------------------------------------------|------|------|------|-------------|

| WFLASH                | CPU wait states, running from flash, cache disabled         | 0    |      | 2    |             |

| WFLASHCACHE           | CPU wait states, running from flash, cache enabled          | 0    |      | 3    |             |

| WRAM                  | CPU wait states, running from RAM                           |      |      | 0    |             |

| IDDFLASHCACHE         | CPU current, running from flash, cache enabled, LDO         |      | 7.4  |      | mA          |

| IDDFLASHCACHEDCD<br>C | CPU current, running from flash, cache enabled, DCDC 3V     |      | 3.7  |      | mA          |

| IDDFLASH              | CPU current, running from flash, cache disabled, LDO        |      | 8.0  |      | mA          |

| IDDFLASHDCDC          | CPU current, running from flash, cache disabled, DCDC 3V    |      | 3.9  |      | mA          |

| IDDRAM                | CPU current, running from RAM, LDO                          |      | 6.7  |      | mA          |

| IDDRAMDCDC            | CPU current, running from RAM, DCDC 3V                      |      | 3.3  |      | mA          |

| IDDFLASH/MHz          | CPU efficiency, running from flash, cache enabled, LDO      |      | 125  |      | μΑ/<br>MHz  |

| IDDFLASHDCDC/MHz      | CPU efficiency, running from flash, cache enabled, DCDC 3V  |      | 58   |      | μΑ/<br>MHz  |

| CMFLASH               | CoreMark5, running from flash, cache enabled                |      | 215  |      | Core        |

| CMFLASH/MHz           | CoreMark per MHz, running from flash, cache enabled         |      | 3.36 |      | Core<br>MHz |

| CMFLASH/mA            | CoreMark per mA, running from flash, cache enabled, DCDC 3V |      | 58   |      | Core<br>mA  |

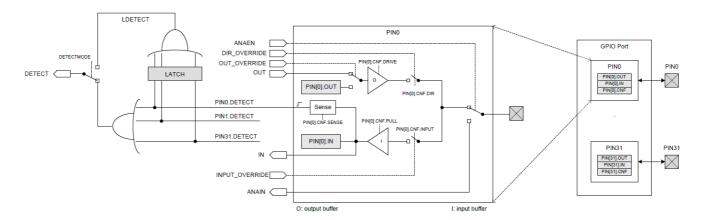

### 3. GPIO — General purpose input/output

The general purpose input/output (GPIO) is organized as one port with up to 32 I/Os (dependent on package) enabling access and control of up to 32 pins through one port. Each GPIO can be accessed individually.

GPIO has the following user-configurable features:

- · Up to 32 GPIO

- 8 GPIO with Analog channels for SAADC, COMP or LPCOMP inputs

- · Configurable output drive strength

- · Internal pull-up and pull-down resistors

- Wake-up from high or low level triggers on all pins

- Trigger interrupt on state changes on any pin

- All pins can be used by the PPI task/event system

- One or more GPIO outputs can be controlled through PPI and GPIOTE channels

- · All pins can be individually mapped to interface blocks for layout flexibility

- GPIO state changes captured on SENSE signal can be stored by LATCH register

The GPIO Port peripheral implements up to 32 pins, PIN0through PIN31. Each of these pins can be individually configured in the PIN\_CNF[n] registers (n=0..31).

The following parameters can be configured through these registers:

- Direction

- Drive strength

- Enabling of pull-up and pull-down resistors

- Pin sensing

- Input buffer disconnect

- Analog input (for selected pins)

Figure: GPIO Port and the GPIO pin details

**GPIO Electrical Specification**

| Symbol    | Description                                                         | Min.         | Тур. | Max.         | Units |

|-----------|---------------------------------------------------------------------|--------------|------|--------------|-------|

| VIH       | Input high voltage                                                  | 0.7 x<br>VDD |      | VDD          | V     |

| VIL       | Input low voltage                                                   | VSS          |      | 0.3 x<br>VDD | V     |

| VOH,SD    | Output high voltage, standard drive, 0.5 mA, VDD ≥1.7               | VDD-0.4      |      | VDD          | V     |

| VOH,HDH   | Output high voltage, high drive, 5 mA, VDD >= 2.7 V                 | VDD-0.4      |      | VDD          | V     |

| VOH,HDL   | Output high voltage, high drive, 3 mA, VDD >= 1.7 V                 | VDD-0.4      |      | VDD          | V     |

| VOL,SD    | Output low voltage, standard drive, 0.5 mA, VDD ≥1.7                | VSS          |      | VSS+0.4      | V     |

| VOL,HDH   | Output low voltage, high drive, 5 mA, VDD >= 2.7 V                  | VSS          |      | VSS+0.4      | V     |

| VOL,HDL   | Output low voltage, high drive, 3 mA, VDD >= 1.7 V                  | VSS          |      | VSS+0.4      | V     |

| IOL,SD    | Current at VSS+0.4 V, output set low, standard drive, VDD ≥1.7      | 1            | 2    | 4            | mA    |

| IOL,HDH   | Current at VSS+0.4 V, output set low, high drive, VDD >= 2.7 V      | 6            | 10   | 15           | mA    |

| IOL,HDL   | Current at VSS+0.4 V, output set low, high drive, VDD >= 1.7 V      | 3            |      |              | mA    |

| IOH,SD    | Current at VDD-0.4 V, output set high, standard drive, VDD ≥1.7     | 1            | 2    | 4            | mA    |

| IOH,HDH   | Current at VDD-0.4 V, output set high, high drive, VDD >= 2.7 V     | 6            | 9    | 14           | mA    |

| IOH,HDL   | Current at VDD-0.4 V, output set high, high drive, VDD >= 1.7 V     | 3            |      |              | mA    |

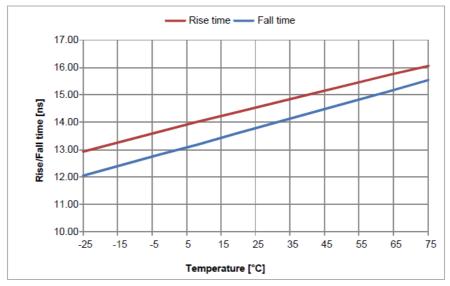

| tRF,15pF  | Rise/fall time, low drive mode, 10-90%, 15 pF load $^{\! 1}$        |              | 9    |              | ns    |

| tRF,25pF  | Rise/fall time, low drive mode, 10-90%, 25 pF<br>load <sup>1</sup>  |              | 13   |              | ns    |

| tRF,50pF  | Rise/fall time, low drive mode, 10-90%, 50 pF<br>load <sup>1</sup>  |              | 25   |              | ns    |

| tHRF,15pF | Rise/Fall time, high drive mode, 10-90%, 15 pF<br>load <sup>1</sup> |              | 4    |              | ns    |

| tHRF,25pF | Rise/Fall time, high drive mode, 10-90%, 25 pF<br>load <sup>1</sup> |              | 5    |              | ns    |

| tHRF,50pF | Rise/Fall time, high drive mode, 10-90%, 50 pF<br>load <sup>1</sup> |              | 8    |              | ns    |

| RPU       | Pull-up resistance                                                  | 11           | 13   | 16           | kΩ    |

| RPD       | Pull-down resistance                                                | 11           | 13   | 16           | kΩ    |

| CPAD      | Pad capacitance                                                     |              | 3    |              | pF    |

| CPAD_NFC  | Pad capacitance on NFC pads                                         |              | 4    |              | pF    |

| INFC_LEAK | Leakage current between NFC pads when driven to different states    |              | 2    | 10           | μΑ    |

The current drawn from the battery when GPIO is active as an output is calculated as follows: IGPIO=VDD Cload f

C<sub>load</sub> being the load capacitance and "f" is the switching frequency.

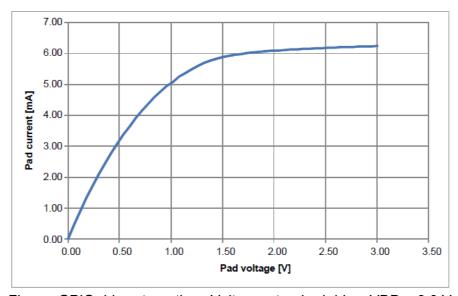

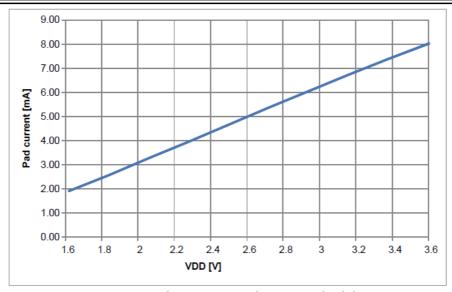

Figure: GPIO drive strength vs Voltage, standard drive, VDD = 3.0 V

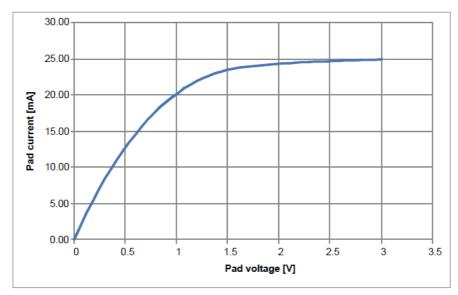

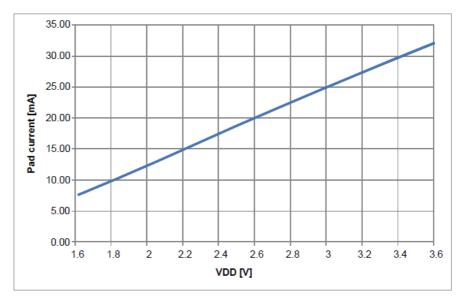

Figure: GPIO drive strength vs Voltage, high drive, VDD = 3.0 V

Figure: Max sink current vs Voltage, standard drive

Figure: Max sink current vs Voltage, high drive

Figure: Rise and fall time vs Temperature, 10%-90%, 25pF load capacitance, VDD = 3.0 V

### 4、RADIO — 2.4 GHz Radio

The RADIO contains a 2.4 GHz radio receiver and a 2.4 GHz radio transmitter that is compatible with Nordic's proprietary 1 Mbps and 2 Mbps radio modes in addition to 1 Mbps and 2 Mbps *Bluetooth*<sup>®</sup> low energy mode.

EasyDMA in combination with an automated packet assembler and packet disassembler, and an automated CRC generator and CRC checker, makes it very easy to configure and use the RADIO. See *Figure: RADIO block diagram* on page 205 for details.

Figure: RADIO block diagram

#### **General Radio Characteristics**

| Symbol        | Description                  | Min. Typ. Max. |      |      | Units |

|---------------|------------------------------|----------------|------|------|-------|

| fOP           | Operating frequencies        | 2360           |      | 2500 | MHz   |

| fPLL,PROG,RES | PLL programming resolution   |                | 2    |      | kHz   |

| fPLL,CH,SP    | PLL channel spacing          |                | 1    |      | MHz   |

| fDELTA,1M     | Frequency deviation @ 1 Msps |                | ±170 |      | kHz   |

| fDELTA,BLE,1M | Frequency deviation @ BLE 1Msps  |   | ±250 |   | kHz  |

|---------------|----------------------------------|---|------|---|------|

| fDELTA,2M     | Frequency deviation @ 2 Msps     |   | ±320 |   | kHz  |

| fDELTA,BLE,2M | Frequency deviation @ BLE 2 Msps |   | ±500 |   | kHz  |

| fskSPS        | On-the-air data rate             | 1 |      | 2 | Msps |

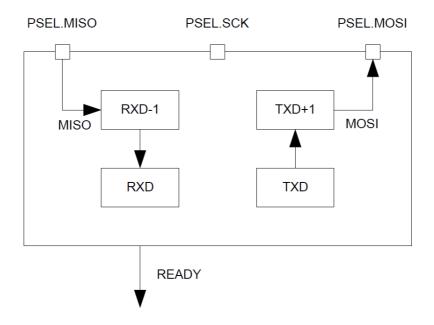

### 5. SPI — Serial peripheral interface master

The SPI master provides a simple CPU interface which includes a TXD register for sending data and an RXD register for receiving data. This section is added for legacy support for now.

Figure: SPI master

RXD-1 and TXD+1 illustrate the double buffered version of RXD and TXD respectively.

#### SPI master mode pin configuration

The different signals SCK, MOSI, and MISO associated with the SPI master are mapped to physical pins.

This mapping is according to the configuration specified in the PSELSCK, PSELMOSI,

and PSELMISO registers respectively. If a value of 0xFFFFFFFF is specified in any of these registers, the associated SPI master signal is not connected to any physical pin. The PSELSCK, PSELMOSI, and PSELMISO registers and their configurations are only used as long as the SPI master is enabled, and retained only as long as the device is in ON mode. PSELSCK, PSELMOSI, and PSELMISO must only be configured when the SPI master is disabled.

To secure correct behavior in the SPI, the pins used by the SPI must be configured in the GPIO peripheral as described in *Table: GPIO configuration* on page 514 prior to enabling the SPI. The SCK must always be connected to a pin, and that pin's input buffer must always be connected for the SPI to work. This configuration must be retained in the GPIO for the selected IOs as long as the SPI is enabled.

Only one peripheral can be assigned to drive a particular GPIO pin at a time, failing to do so may result in unpredictable behavior.

#### **GPIO** configuration

| SPI master signal | SPI master pin           | Direction | Output value        |

|-------------------|--------------------------|-----------|---------------------|

| SCK               | As specified in PSELSCK  | Output    | Same as CONFIG.CPOL |

| MOSI              | As specified in PSELMOSI | Output    | 0                   |

| MISO              | As specified in PSELMISO | Input     | Not applicable      |

#### SPI master interface

| Of Finaster inter | 1400                                                                          |                             |      |      |

|-------------------|-------------------------------------------------------------------------------|-----------------------------|------|------|

| Symbol            | Description                                                                   | Min.                        | Тур. | Max. |

| fspi              | Bit rates for SPI <sup>38</sup>                                               | 8 <sup>39</sup>             | Mbps | fspi |

| ISPI,2Mbps        | Run current for SPI, 2 Mbps                                                   |                             | 50   | μΑ   |

| ISPI,8Mbps        | Run current for SPI, 8 Mbps                                                   |                             | 50   | μΑ   |

| ISPI,IDLE         | Idle current for SPI (STARTed, no CSN activity)                               | <1                          |      | μΑ   |

| tspi,start,lp     | Time from writing TXD register to transmission started, low power mode        | tspi,sta<br>RT,CL<br>+<br>t |      | μs   |

| tSPI,START,CL     | Time from writing TXD register to transmission started, constant latency mode | 1                           |      | μs   |

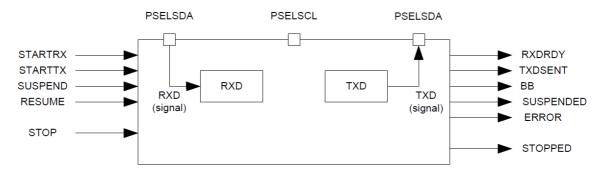

## 6、TWI — I<sup>2</sup>C compatible two-wire interface

The TWI master is compatible with I<sup>2</sup>C operating at 100 kHz and 400 kHz.

Figure: TWI master's main features

#### Master mode pin configuration

The different signals SCL and SDA associated with the TWI master are mapped to physical pins according to the configuration specified in the PSELSCL and PSELSDA registers respectively. If a value of 0xFFFFFFFF is specified in any of these registers, the associated TWI master signal is not connected to any physical pin. The PSELSCL and PSELSDA registers and their configurations are only used as long as the TWI master is enabled, and retained only as long as the device is in ON mode. PSELSCL and PSELSDA must only be configured when the TWI is disabled.

To secure correct signal levels on the pins used by the TWI master when the system is in OFF mode, and when the TWI master is disabled, these pins must be configured in the GPIO peripheral as described in *Table: GPIO configuration* on page 522.

Only one peripheral can be assigned to drive a particular GPIO pin at a time, failing to do so may result in unpredictable behavior.

**Table 125: GPIO configuration**

| TWI master signal | TWI master pin          | Direction | Drive strength | Output value   |

|-------------------|-------------------------|-----------|----------------|----------------|

| SCL               | As specified in PSELSCL | Input     | SOD1           | Not applicable |

| SDA               | As specified in PSELSDA | Input     | SOD1           | Not applicable |

| Symbol        | Description                                                                   | Min. | Тур.           | Max. | Units |

|---------------|-------------------------------------------------------------------------------|------|----------------|------|-------|

| fTWI          | Bit rates for TWI <sup>40</sup>                                               | 100  |                | 400  | kbps  |

| ITWI,100kbps  | Run current for TWI, 100 kbps                                                 |      | 50             |      | μΑ    |

| ITWI,400kbps  | Run current for TWI, 400 kbps                                                 |      | 50             |      | μΑ    |

| tTWI,START,LP | Time from STARTRX/STARTTX task to transmission started, Low power mode        |      | tTWI,S<br>TART |      | μs    |

|               |                                                                               |      | +<br>t         |      |       |

|               |                                                                               |      | L              |      |       |

| tTWI,START,CL | Time from STARTRX/STARTTX task to transmission started, Constant latency mode |      | 1.5            |      | μs    |

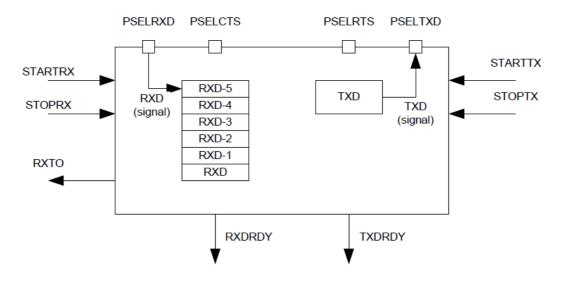

### 7. UART — Universal asynchronous receiver/ transmitter

Figure 160: UART configuration

#### Pin configuration

The different signals RXD, CTS (Clear To Send, active low), RTS (Request To Send, active low), and TXD associated with the UART are mapped to physical pins according to the configuration specified in the PSELRXD, PSELCTS, PSELRTS, and PSELTXD registers respectively.

If a value of 0xFFFFFFF is specified in any of these registers, the associated UART signal will not be connected to any physical pin. The PSELRXD, PSELCTS, PSELRTS, and PSELTXD registers and their configurations are only used as long as the UART is enabled, and retained only for the duration the device is in ON mode. PSELRXD, PSELCTS, PSELRTS and PSELTXD must only be configured when the UART is disabled.

To secure correct signal levels on the pins by the UART when the system is in OFF mode, the pins must be configured in the GPIO peripheral as described in *Pin configuration* on page 531.

Only one peripheral can be assigned to drive a particular GPIO pin at a time. Failing to do so may result in unpredictable behavior.

**Table 128: GPIO configuration**

| UART pin | Direction |        | Output value   |

|----------|-----------|--------|----------------|

| RXD      |           | Input  | Not applicable |

| CTS      |           | Input  | Not applicable |

| RTS      |           | Output | 1              |

| TXD      |           | Output | 1              |

**UART** electrical specification

| Symbol         | Description                                                                   | Min. | Тур.                    | Max. | Units |

|----------------|-------------------------------------------------------------------------------|------|-------------------------|------|-------|

| fuart          | Baud rate for UART $^{41}$ .                                                  |      |                         | 1000 | kbps  |

| IUART1M        | Run current at max baud rate.                                                 |      | 55                      |      | μΑ    |

| lUART115k      | Run current at 115200 bps.                                                    |      | 55                      |      | μΑ    |

| lUART1k2       | Run current at 1200 bps.                                                      |      | 55                      |      | μΑ    |

| IUART,IDLE     | Idle current for UART                                                         |      | 1                       |      | μΑ    |

| tuart,ctsh     | CTS high time                                                                 | 1    |                         |      | μs    |

| tUART,START,LP | Time from STARTRX/STARTTX task to transmission started, low power mode        |      | tuart,<br>STA<br>+<br>t |      | μs    |

| tuart,start,cl | Time from STARTRX/STARTTX task to transmission started, constant latency mode |      | 1                       |      | μs    |

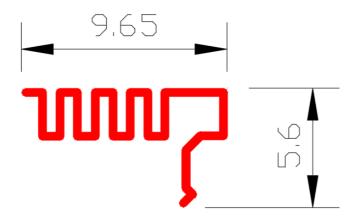

### 8、PCB Printed Antenna Information

#### **PCB Printed Antenna Dimension**

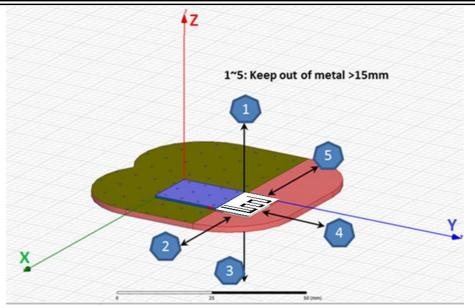

### **Antenna Keep Out Area Example**

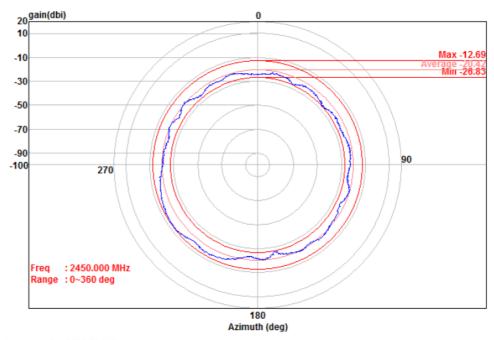

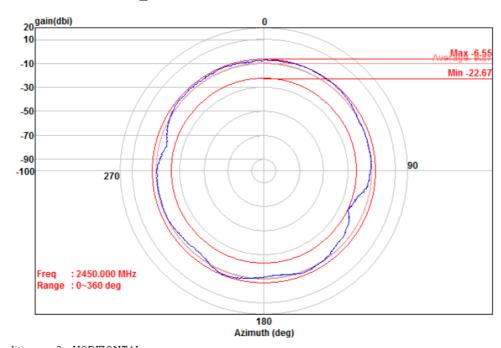

#### **Module Radiation Pattern**

VERTICAL Antenna 2D Radiation Pattern @2450 MHz

Condition : 3m VERTICAL Project Number:

Compy Model Compy : Model : PCB Test Mode : 2450 Test Site : Chamber 966 Temp/Humi : 25/60

#### HORIZONTAL\_Antenna 2D Radiation Pattern @2450 MHz

Condition : 3m HORIZONTAL

Project Number: Сотру :PCB Model

Test Mode : 2450

SUNRI: Test Site : Chamber 966

Temp/Humi : 25/60

### **APPENDIX A: CERTIFICATION NOTICES**

#### **Federal Communications Commission (FCC) Statement**

15.21

You are cautioned that changes or modifications not expressly approved by the part responsible for compliance could void the user's authority to operate the equipment.

#### 15.105(b)

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications.

However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- -Reorient or relocate the receiving antenna.

- -Increase the separation between the equipment and receiver.

- -Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- -Consult the dealer or an experienced radio/TV technician for help.

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

- 1) this device may not cause harmful interference, and

- 2) this device must accept any interference received, including interference that may cause undesired operation

of the device.

#### **FCC RF Radiation Exposure Statement**

This equipment complies with FCC radiation exposure limits set forth for an uncontrolled environment.

This equipment should be installed and operated with minimum distance 20cm between the radiator & your body.

This transmitter must not be co-located or operating in conjunction with any other antenna or transmitter.

Note: The end product shall has the words "Contains Transmitter Module FCC ID: 2AMPPAI00240"

#### Canada, Industry Canada (IC)

This Class B digital apparatus complies with Canadian ICES-003 Cet appareil numérique de classe B est conforme à la norme NMB-003.

# Le present appareil est conforme aux CNR d'Industrie Canada applicables auxappareils radio exempts de licence.L'exploitation est autorisée aux deux conditions suivantes:

- (1) l'appareil ne doit pas produire de brouillage, et

- (2) l'utilisateur de l'appareil doit accepter tout brouillage adioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

#### Déclaration d'exposition aux radiations:

Cet équipement est conforme aux limites d'exposition au rayonnement ISED établies pour un environnement non contrôlé.

Cet équipement doit être installé et utilisé à une distance minimale de 20 cm entre le radiateur et votre corps.

Cet émetteur ne doit pas être co-localisé ou fonctionner en conjonction avec une autre antenne ou un autre émetteur.

#### **ICES-003 RF Radiation Exposure Statement**

This equipment complies with ICES-003 radiation exposure limits set forth for an uncontrolled environment.

This equipment should be installed and operated with minimum distance 20cm between the radiator & your body.

This transmitter must not be co-located or operating in conjunction with any other antenna or transmitter.

Note: The end product shall has the words "Contains Transmitter Module IC: 11471A-AI00240"

#### (Modular approval) End Product Labeling:

The final end product must be labeled in a visible area with the following: "Contains IC: 11471A-AI00240".

#### **OEMstatement**

The Original Equipment Manufacturer (OEM) must ensure that the OEM modular transmitter must be labeled with its own FCC ID number. This includes a clearly visible label on the outside of the final product enclosure that displays the contents shown below. If the FCC ID is not visible when the equipment is installed inside another device, then the outside of the device into which the equipment is installed must also display a label referring to the enclosed equipment

The end product with this module may subject to perform FCC part 15 unintentional emission test requirement and be properly authorized.

This device is intended for OEM integrator only This radio transmitter (192170139/AA/00) has been approved by Innovation, Science and Economic Development Canada to operate with the antenna types listed Below, with the maximum permissible gain indicated. Antenna types not included in this list that Have a gain greater than the maximum gain indicated for any type listed are strictly prohibited for use with this device.

AI00240: PCB Antenna, 1 dBi

### APPENDIX B: LABEL FOR FINISHED PRODUCT

Contains Transmitter Module FCC ID: 2AMPPAI00240

and IC: 11471A-AI00240

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

- 1) this device may not cause harmful interference, and

- 2) this device must accept any interference received, including interference that may cause the device undesired operation of.

### **Version Information**

| Date       | number | Description     |

|------------|--------|-----------------|

| 2021.07.22 | V1.0   | Initial Version |

|            |        |                 |

|            |        |                 |

|            |        |                 |

|            |        |                 |

|            |        |                 |

<< BLANK >>