High-performance 2.4 GHz Multi-protocol Wireless MCUs and Modules, supporting Bluetooth Low Energy and 802.15.4 protocols with 32-bit ARM® Cortex®-M4F, 2 Msps 12-bit ADC Data Sheet

### Introduction

The PIC32CX-BZ2 family is a general purpose, low-cost, 32-bit Microcontroller (MCU) family of devices supporting multi-protocol wireless interfaces (Bluetooth® and Zigbee®), hardware-based security accelerator, transceiver and Power Management Unit (PMU).

The WBZ45 Module is a series of fully RF-certified wireless modules that contain the PIC32CX-BZ2 wireless MCUs with the following antenna options:

- PCB Antenna

- · u.FL Connector for External Antenna

In addition to the Bluetooth Low Energy (Bluetooth 5.2) and Zigbee (Zigbee 3.0) wireless protocol support, the PIC32CX-BZ2 devices and the WBZ45 modules also support a rich set of standard MCU peripherals, such as Analog-to-Digital Converter (ADC), Serial Peripheral Interface (SPI), Inter-Integrated Circuit (I<sup>2</sup>C), Quad I/O Serial Peripheral Interface (QSPI), Universal Asynchronous Receiver-Transmitter (UART) and Serial Wire Debug (SWD).

### PIC32CX-BZ2 SoC Family Features

The following section lists the PIC32CX-BZ2 SoC related features:

### Operating Conditions of MCUs

- 1.9V to 3.6V, -40°C to +125°C, DC to 64 MHz

- AEC Q100 Grade 1 qualified

### Core: 64 MHz ARM® Cortex®-M4

- 3.35 Coremark<sup>®</sup>/MHz

- · 4 KB Combined Instruction Cache and Data Cache

- 8-Zone Memory Protection Unit (MPU)

- Thumb<sup>®</sup>-2 Instruction Set

- · Digital Signal Processing ASE Rev 2

- Nested Vector Interrupt Controller (NVIC)

- Embedded Trace Module (ETM) with Instruction Trace Stream

- Core Sight Embedded Trace Buffer (ETB)

- Trace Port Interface Unit (TPIU)

- IEEE<sup>®</sup> 754-Compliant Floating Point Unit (FPU)

### **Memories**

- 1 MB On-Chip Self-Programmable Flash with:

- Error Correction Code (ECC)

- Prefetch module to speed up Flash accesses

- 20-years of data retention support

- · 32 KB NVR Flash (8 Sectors)

- Private/public boot code and data

- NV calibration data

- 128 KB Multi-Port Programmable QoS SRAM Main Memory

- 64 KB of Error Correction Code (ECC) RAM option

- Up to 4 KB of Tightly Coupled Memory (TCM)

- · Up to 8 KB Backup SRAM

- Single 32-bit Backup Register

### System

- Power-on Reset (POR) and Brown-out Detect (BOD)

- Internal and External Clock Options

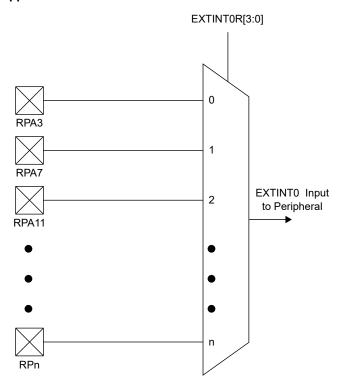

- External Interrupt Controller (EIC)

- · Up to four External Interrupts

- · One Non-maskable Interrupt

- · 2-pin Serial Wire Debug (SWD) Programming, Test and Debugging Interface

### **Supported Connectivity Standards**

- Complies with:

- Bluetooth v5.2

- IEEE 802.15.4, Zigbee 3.0

- ETSI EN 300 328 and EN 300 440 Class 2

- FCC CFR47 Part 15 and ARIB STD-T66

### **Power Supply**

- Integrated PMU with:

- Buck (DC-DC/switching) mode; supports High Power (PWM) and Low Power (PSK) mode

- MLDO (linear) mode

- On-board 1.2V Voltage Regulator (CLDO)

- Power-on Reset (POR) and Brown-out Detect (BOD) on 3.3V and 1.2V Rails

- · Run, Idle, Dream, Sleep, Deep Sleep and Extreme Deep Sleep Modes

- · Sleep Walking Peripherals

- Embedded Buck/LDO Regulator Supporting On-the-Fly (OTF) Selection

#### 2.4 GHz RF Transceiver

- Integrated 2.4 GHz Ultra-low Power RF Transceiver shared among Bluetooth, Zigbee Modems, Link (MAC)

Controllers and Proprietary Modulation Schemes

- Integrated 16 MHz ±20 ppm Crystal Oscillator (External Low Cost Crystal)

- Two PA Design Architecture (LPA (+4 dBm) and MPA (+12 dBm)) to Improve TX Power Efficiency

- Low RBOM Two-port TRX RFFE Architecture

- Integrated balun (single-ended RF output) and TRX switch

- Hardware Radio Arbiter with Programmable QoS:

- Resolution per packet level

- Time-division coexistence between Bluetooth and 802.15.4

- Based on shared transceiver and antenna

- Maintains connections of 802.15.4 and Bluetooth simultaneously

#### **Bluetooth**

- · Bluetooth Low Energy 5.2 Certified

- Up to +12 dBm Programmable Transmit Output Power

- Typical Receiver Power Sensitivity:

- -95 dBm for Bluetooth Low Energy 1 Mbps

- 92 dBm for Bluetooth Low Energy 2 Mbps

- 102 dBm for Bluetooth Low Energy 125 Kbps

- -99 dBm for Bluetooth Low Energy 500 Kbps

- Digital RSSI indicator (-50 dBm to -90 dBm)

- · Bluetooth Supported Features:

- 2M uncoded PHY

- Long range (Coded PHY)

- Channel selection algorithm #2

- Advertising extensions, offloads CPU with hardware-based scheduler

- High duty cycle non-connectible advertising

- Data length extensions

- Secure connections

- Privacy upgrades (with hardware white-list support)

- ECDH P256 Hardware Engine for Link Key Generation when Bluetooth Pairing

- AES128 Hardware Module for Real-Time Bluetooth Payload Data Encryption

- · Preprogrammed MAC Address

- Bluetooth Qualification Test Facility (BQTF) Certification

- · Bluetooth Low Energy Profiles:

- Bluetooth Low Energy peripheral and central roles

- Bluetooth Low Energy APIs for application layer to implement standard or customize GATT based profiles/ services

- Microchip Transparent UART Service

- Battery Service

- Device Information Service

- Custom Service

- Multi-link and multi-role

- · Bluetooth Low Energy Services:

- Provisioning

- Over-the-Air (OTA) update (also known as DFU)

- Advertisement/Beacon

- Personalized configuration

- Alert notification service

### 802.15.4/Zigbee Modulation Scheme

• 802.15.4/Zigbee Physical Layer Service Unit (PSDU) Data Rate: 250 Kbps

- · Programmable RX Mode

- -103 dBm RX sensitivity in the Continuous mode

- -98 dBm sensitivity in RPC mode

- RPC mode provides lower power consumption in RX mode to support California Green Energy Specification at the system level

- TX Output Power up to +12 dBm

- Hardware Assisted MAC

- Auto acknowledge

- Auto retry

- Channel access back-off

- · Preprogrammed MAC Address

- · SFD Detection; Spreading; De-spreading; Framing; CRC-16 Computation

- · Independent TX/RX Buffers for Improved CPU Offloading While Handling Zigbee Data

- 128-byte TX and 128-byte RX frame buffer

- · Hardware Security

- Advanced Encryption Standard (AES)

- True Random Number Generator (TRNG)

- Zigbee Stack Support

- Zigbee 3.0 ready

- Zigbee Pro 2017

- Zigbee green power support (proxy, sink and multi-sensor)

### **Proprietary**

- Proprietary Data Rates: 500 Kbps, 1 Mbps and 2 Mbps

- TX Output Power up to +12 dBm

- Receiver Sensitivity up to -96 dBm

- Hardware Assisted MAC

- Auto acknowledge

- Auto retry

- Channel access back-off

- · SFD Detection; Spreading; De-spreading; Framing; CRC-16 Computation

- · Independent TX/RX Buffers for Improved CPU Offloading While Handling Zigbee Data

- 128-byte TX and 128-byte RX frame buffer

- · Hardware Security

- Advanced Encryption Standard (AES)

- True Random Number Generator (TRNG)

### **High Performance Peripherals**

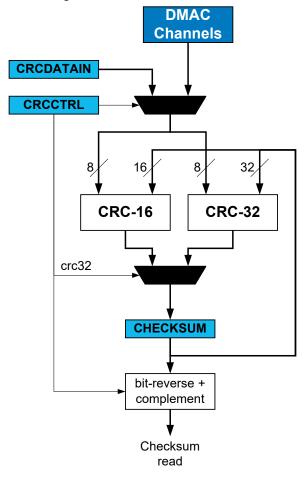

- 16-Channel Direct Memory Access Controller (DMAC)

- Built-in CRC with memory CRC generation/monitor hardware support

- One Quad I/O Serial Peripheral Interface (QSPI)

- execute-In-Place (xIP) support

- Dedicated AHB memory zone

### System Peripherals

32-Channel Event System

- All channels can be connected to any event generator

- All channels provide a pure asynchronous path

- Twelve channels support synchronous and re-synchronous

- Four Serial Communication Interfaces (SERCOM), Each Configurable to Operate as:

- USART with full-duplex and single-wire half-duplex configuration

- ISO7816

- I<sup>2</sup>C up to 1 MHz (three SERCOMs support I<sup>2</sup>C)

- LIN Commander/Responder

- RS485

- SPI inter-byte space

- Four 16-bit Timers/Counters (TC), Each Configurable as:

- 16-bit TC with two compare/capture channels

- 8-bit TC with two compare/capture channels

- 32-bit TC with two compare/capture channels

- · Two 24-bit Timer/Counters for Control (TCC) with Extended Functions:

- Up to six compare channels with optional complementary output

- Generation of synchronized Pulse Width Modulation (PWM) pattern across port pins

- Deterministic fault protection, fast decay and configurable dead-time between complementary output

- Dithering that increases resolution with up to 5 bits and reduces quantization error

- One 16-bit Timer/Counters for Control (TCC) with Extended Functions:

- Up to two compare channels with optional complementary output

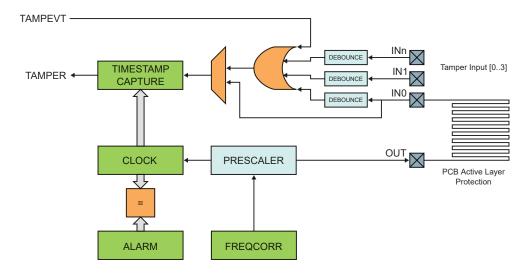

- 32-bit Real Time Counter (RTCC) with Clock/Calendar Function

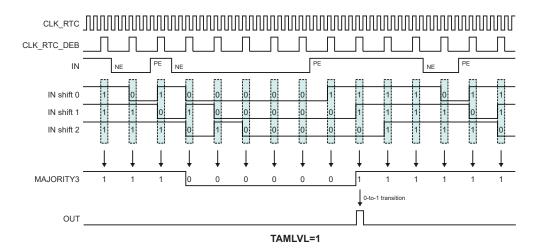

- · Up to one Wake-up Pin with Tamper Detection and Debouncing Filter

- · Watchdog Timer (WDT) with Window Mode

- Deadman Timer (DMT)

- CRC-32 Generator

- Frequency Meter (FREQM)

- Two Configurable Custom Logic (CCL)

- · One Analog Comparator (AC) with Window Compare function

- One Temperature Sensor (Die Temperature)

### **Advanced Analog**

- 12-bit ADC SAR Module (ADC):

- Up to Eight Analog Channels

- Up to Two MSPS conversion rate

- Multiple trigger sources

- Supports die temperature sensor built into RF-Analog (not an external "ambient" temperature sensor)

- Two Analog Comparator (AC) with Window Compare Function or single Analog Comparator

- One dedicated AC and second AC is shared with PMU Controller

### Security

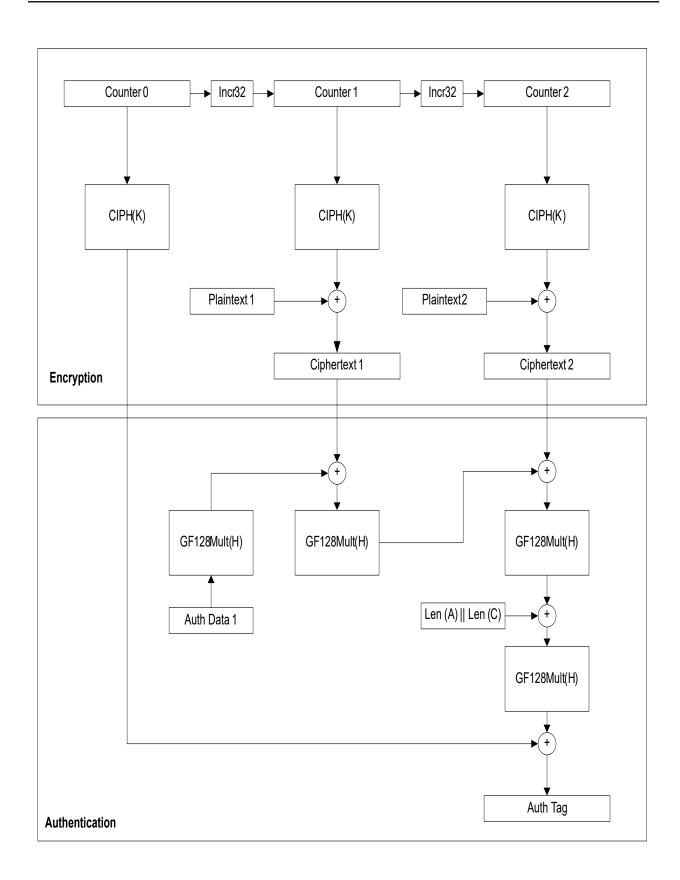

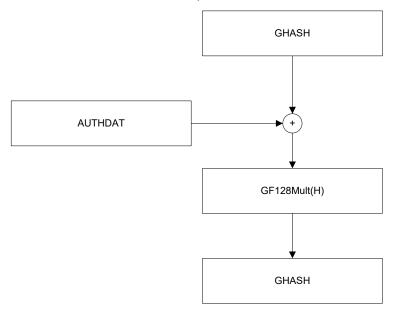

- AES Engine with Support for 128/192/256-bit Cryptographic Key

- · One AES with 256-bit Key Length and up to 2 MB/s Data Rate

- Five confidential modes of operation (ECB, CBC, CFB, OFB and CTR)

- Supports counter with CBC-MAC mode

- Galois Counter Mode (GCM)

- True Random Number Generator (TRNG)

- Public Key Cryptography Controller (PUKCC) and Associated Classical Public Key Cryptography Library (PUKCL)

- RSA and DSA algorithm

- Elliptic Curves Cryptography (ECC), ECC GF (2n) and ECCGF (p)

- · Integrity Check Module (ICM) Based on Secure Hash Algorithm (SHA1, SHA224 and SHA256), DMA Assisted

### **Oscillators**

- 16 MHz, ±20 PPM Crystal/Resonator Oscillator or External Clock (POSC) for 2.4G RF Transceiver

- · Shared System PLL with Bluetooth/Zigbee RF Data Converter PLL

- 32.768 kHz Ultra-low Power Internal Oscillator

- Higher Accuracy 32.768 kHz, ±250 ppm Clock Options

- POSC derived 32 kHz clock

- 32.768 kHz crystal/resonator oscillator (SOSC)

- External 32.768 kHz clock source

- 8 MHz Internal RC Oscillator (FRC)

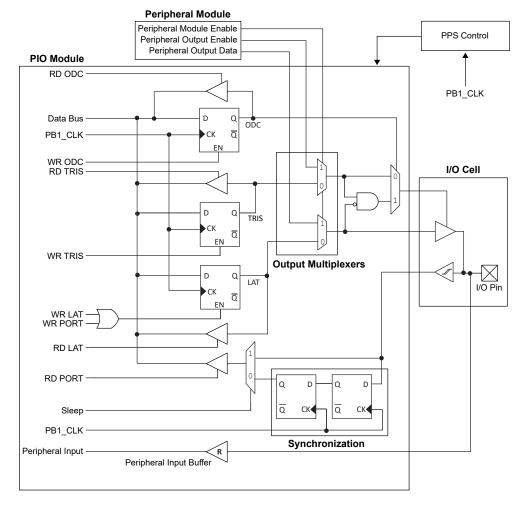

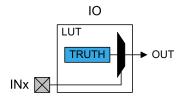

#### I/O

- · Flexible Peripheral Pin Select (PPS) Support

- · High-Current Sink/Source on Most I/O Pins

- · Configurable Open-Drain Output on Digital I/O Pins

- Up to 27 Programmable I/O Pins

### **Package**

- PIC32CX1012BZ25048 Package:

- 48-pin QFN

- Size 7 mm x 7 mm x 0.9 mm

- PIC32CX1012BZ25032 Package:

- 32-pin QFN

- Size 5 mm x 5 mm x 1 mm

#### **WBZ45 Module Features**

The WBZ45 modules are wireless MCU modules with BLE 5.2 compliant and Zigbee 3.1 Radio.

The following section lists the WBZ45 Module related features, which complement SoC features:

### **WBZ45 Module Variants**

- WBZ451 based on (PIC32CX1012BZ25048 SoC)

- WBZ451PE (PCB)

- WBZ451UE (u.FL)

- WBZ450 based on (PIC32CX1012BZ25032 SoC)

- WBZ450PC (PCB)

- WBZ450UC (u.FL)

- WBZ450PE (PCB)

- WBZ450UE (u.FL)

#### Antenna

- · On-Board PCB Antenna

- External Antenna

### **Clock Management**

· Integrated 16 MHz POSC

### System Peripheral, Advanced Analog and Security

· All features of SoC are accessible

### **Package and Operating Conditions**

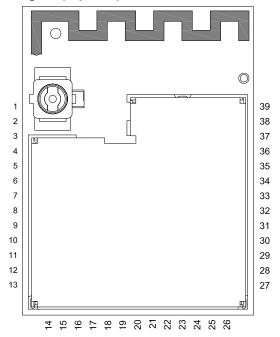

- WBZ451

- 39-pin SMD package with Shield CAN

- Size 15.5 mm x 20.7 mm x 2.8 mm

- WBZ450

- 30-pin SMD package with Shield CAN

- Size 13.4 mm x 18.7 mm x 2.8 mm

- · Operating Conditions

- 1.9V to 3.6V, -40°C to +85°C, DC to 64 MHz

### **Certifications**

- · Certified to FCC, ISED and CE Radio Regulations

- RoHS and REACH Compliant

**Note:** Traditional LIN documentation uses the terminology "Master" and "Slave". The equivalent Microchip terminology used in this document is "Commander" and "Responder", respectively.

### **Table of Contents**

| Intr | roduction                                                 | 1  |

|------|-----------------------------------------------------------|----|

| PIC  | C32CX-BZ2 SoC Family Features                             | 1  |

|      | Operating Conditions of MCUs                              | 1  |

|      | Core: 64 MHz ARM <sup>®</sup> Cortex <sup>®</sup> -M4     | 1  |

|      | Memories                                                  | 2  |

|      | System                                                    | 2  |

|      | Supported Connectivity Standards                          | 2  |

|      | Power Supply                                              | 2  |

|      | 2.4 GHz RF Transceiver                                    | 2  |

|      | Bluetooth                                                 | 3  |

|      | 802.15.4/Zigbee Modulation Scheme                         | 3  |

|      | Proprietary                                               | 4  |

|      | High Performance Peripherals                              | 4  |

|      | System Peripherals                                        | 4  |

|      | Advanced Analog                                           | 5  |

|      | Security                                                  | 5  |

|      | Oscillators                                               | 6  |

|      | I/O                                                       | 6  |

|      | Package                                                   | 6  |

| WE   | 3Z45 Module Features                                      | 6  |

|      | WBZ45 Module Variants                                     | 6  |

|      | 7                                                         |    |

|      | 7                                                         |    |

|      | System Peripheral, Advanced Analog and Security           | 7  |

|      | Package and Operating Conditions                          | 7  |

|      | Certifications                                            | 7  |

| 1.   | Ordering Information                                      | 18 |

|      | 1.1. PIC32CXBZ2 SoC and WBZ45 Module Ordering Information | 18 |

| 2.   | Configuration Summary                                     | 19 |

| 3.   | PIC32CX-BZ2 SoC Description                               | 20 |

|      | 3.1. PIC32CX-BZ2 SoC Block Diagram                        | 20 |

|      | 3.2. Pinout Diagram                                       | 20 |

| 4.   | WBZ45 Module Description                                  | 22 |

|      | 4.1. Pinout Diagram                                       | 22 |

|      | 4.2. Basic Connection Requirement                         | 23 |

|      | 4.3. WBZ45 Module Placement Guidelines                    | 25 |

|      | 4.4. WBZ45 Module Routing Guidelines                      | 26 |

|      | 4.5. WBZ45 Module RF Considerations                       | 27 |

|      | 4.6. WBZ45 Module Antenna Considerations                  | 27 |

|      | 4.7. WBZ45 Module Reflow Profile Information              | 29 |

|      | 4.8. WBZ45 Module Assembly Considerations                 | 30 |

|      |                                                           |    |

| 5.  | Pinou                                     | at and Signal Descriptions List            | 31  |  |  |  |  |  |  |  |

|-----|-------------------------------------------|--------------------------------------------|-----|--|--|--|--|--|--|--|

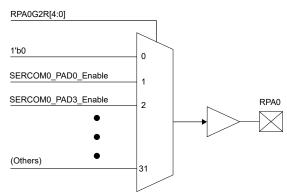

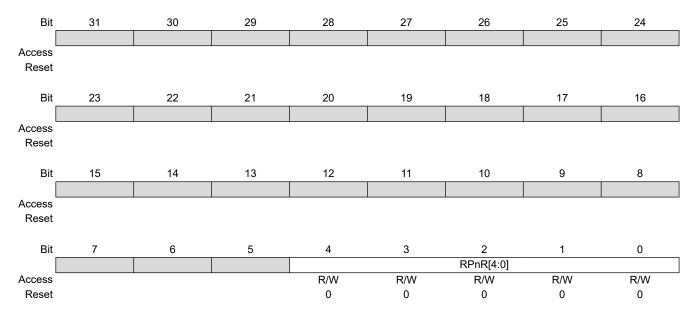

| 6.  | I/O Ports and Peripheral Pin Select (PPS) |                                            |     |  |  |  |  |  |  |  |

|     | 6.1.                                      | Control Registers                          | 34  |  |  |  |  |  |  |  |

|     | 6.2.                                      | Peripheral Pin Select (PPS)                | 36  |  |  |  |  |  |  |  |

|     | 6.3.                                      | Function Priority for Device Pins          | 49  |  |  |  |  |  |  |  |

|     | 6.4.                                      | I/O Ports Control Registers                | 55  |  |  |  |  |  |  |  |

|     | 6.5.                                      | Operation in Power Saving Modes            | 72  |  |  |  |  |  |  |  |

|     | 6.6.                                      | Results of Various Resets                  | 73  |  |  |  |  |  |  |  |

| 7.  | Powe                                      | r Subsystem                                | 74  |  |  |  |  |  |  |  |

|     | 7.1.                                      | Block Diagram                              | 74  |  |  |  |  |  |  |  |

|     | 7.2.                                      | Voltage Regulators                         | 75  |  |  |  |  |  |  |  |

|     | 7.3.                                      | Power Supply Modes                         | 75  |  |  |  |  |  |  |  |

|     | 7.4.                                      | Typical Power Supply Connection for SoC    | 76  |  |  |  |  |  |  |  |

|     | 7.5.                                      | Typical Power Supply Connection for Module | 76  |  |  |  |  |  |  |  |

|     | 7.6.                                      | Power-Up Sequence                          | 77  |  |  |  |  |  |  |  |

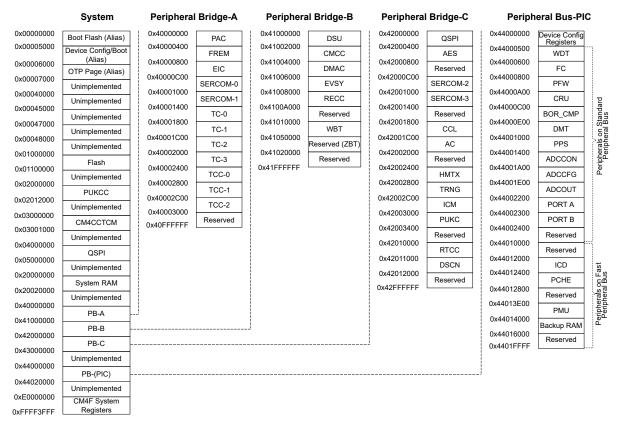

| 8.  | Produ                                     | uct Memory Mapping Overview                | 78  |  |  |  |  |  |  |  |

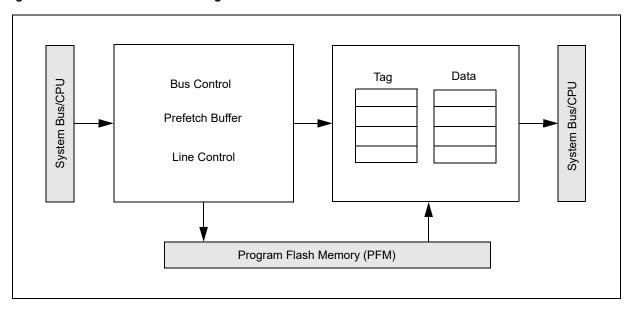

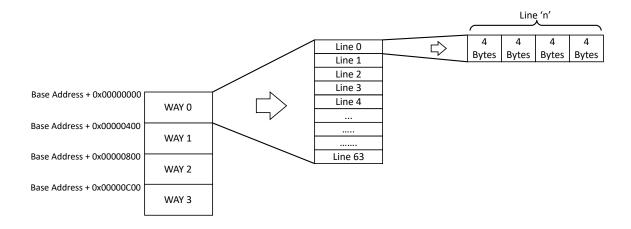

| 9.  | Prefetch Cache (PCHE)                     |                                            |     |  |  |  |  |  |  |  |

|     | 9.1.                                      | Introduction                               | 81  |  |  |  |  |  |  |  |

|     | 9.2.                                      | Features                                   | 81  |  |  |  |  |  |  |  |

|     | 9.3.                                      | Overview                                   | 81  |  |  |  |  |  |  |  |

|     | 9.4.                                      | Prefetch Behavior                          | 83  |  |  |  |  |  |  |  |

|     | 9.5.                                      | Configurations                             | 83  |  |  |  |  |  |  |  |

|     | 9.6.                                      | Predictive Prefetch Behavior               | 84  |  |  |  |  |  |  |  |

|     | 9.7.                                      | Coherency Support                          | 84  |  |  |  |  |  |  |  |

|     | 9.8.                                      | Effects of Reset                           | 84  |  |  |  |  |  |  |  |

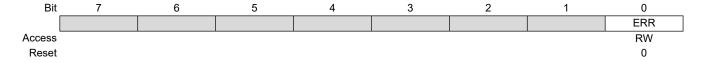

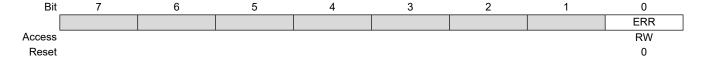

|     | 9.9.                                      | Error Conditions                           | 85  |  |  |  |  |  |  |  |

|     | 9.10.                                     | Operation in Power-saving Modes            | 85  |  |  |  |  |  |  |  |

|     |                                           | · ·                                        |     |  |  |  |  |  |  |  |

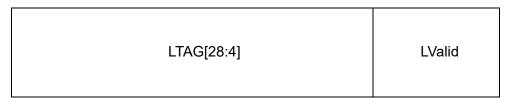

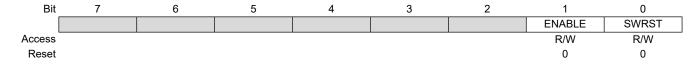

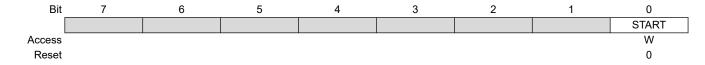

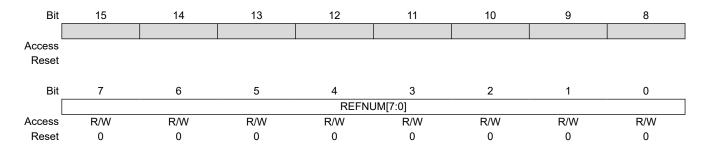

|     | 9.12.                                     | Register Description                       | 87  |  |  |  |  |  |  |  |

| 10. | . Processor and Architecture              |                                            |     |  |  |  |  |  |  |  |

|     | 10.1.                                     | Cortex M4 Processor                        | 94  |  |  |  |  |  |  |  |

|     | 10.2.                                     | Nested Vector Interrupt Controller (NVIC)  | 96  |  |  |  |  |  |  |  |

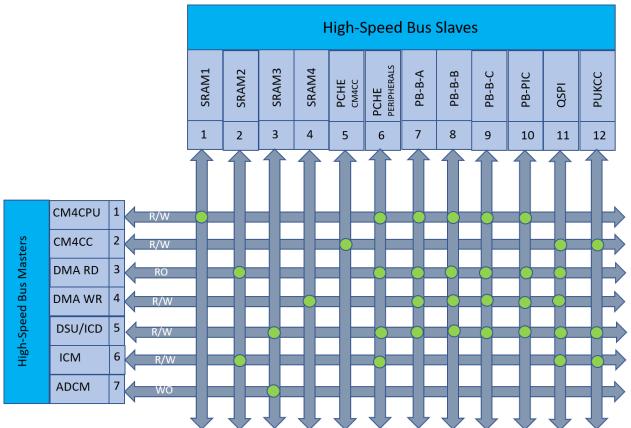

|     |                                           | High-Speed Bus System                      |     |  |  |  |  |  |  |  |

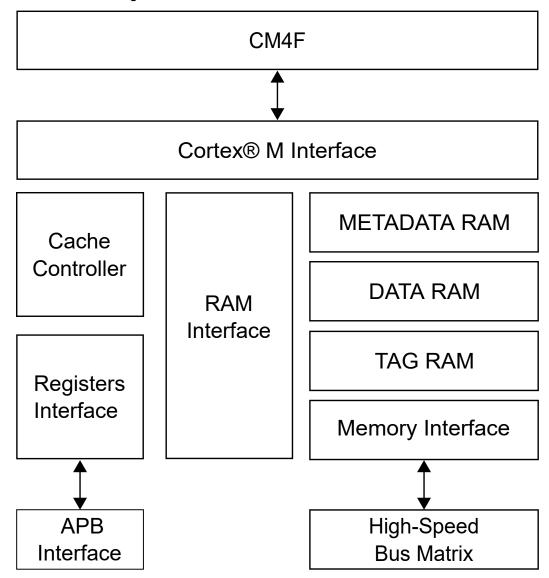

| 11. | Corte                                     | x M Cache Controller (CMCC)                | 104 |  |  |  |  |  |  |  |

|     | 11.1.                                     | Overview                                   | 104 |  |  |  |  |  |  |  |

|     | 11.2.                                     | Features                                   | 104 |  |  |  |  |  |  |  |

|     | 11.3.                                     | Block Diagram                              | 105 |  |  |  |  |  |  |  |

|     |                                           | Signal Description                         |     |  |  |  |  |  |  |  |

|     |                                           | Product Dependencies                       |     |  |  |  |  |  |  |  |

|     |                                           | •                                          |     |  |  |  |  |  |  |  |

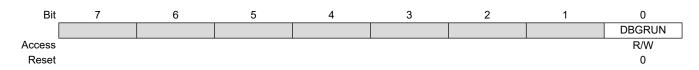

|     |                                           | DEBUG Mode                                 |     |  |  |  |  |  |  |  |

|     |                                           | RAM Properties                             |     |  |  |  |  |  |  |  |

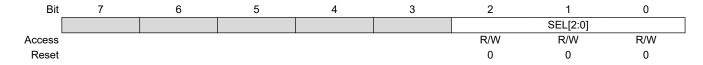

|     |                                           | Register Summary                           |     |  |  |  |  |  |  |  |

|     |                                           |                                            |     |  |  |  |  |  |  |  |

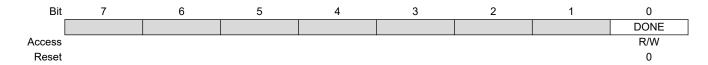

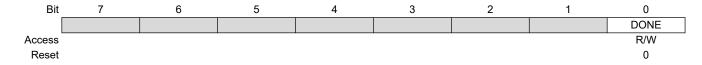

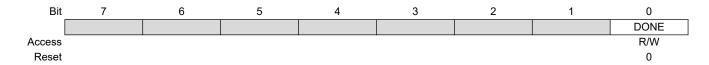

|     | 11.10. Register Description                           | 111 |

|-----|-------------------------------------------------------|-----|

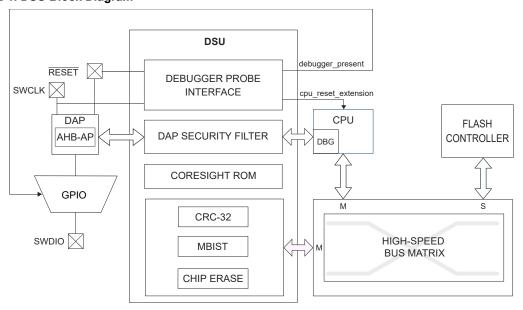

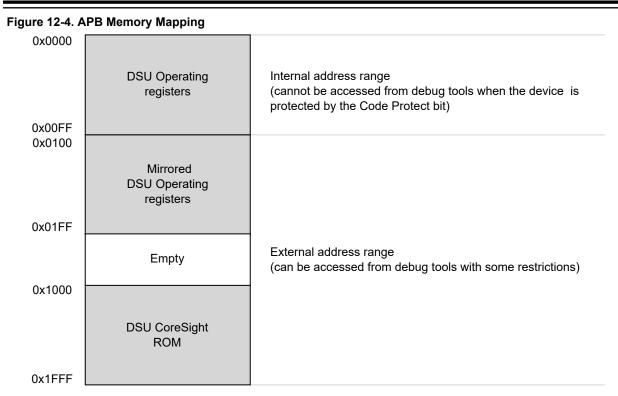

| 12. | Device Service Unit (DSU)                             | 124 |

|     | 12.1. Overview                                        | 124 |

|     | 12.2. Features                                        | 124 |

|     | 12.3. Block Diagram                                   | 124 |

|     | 12.4. Signal Description                              | 124 |

|     | 12.5. Product Dependencies                            | 125 |

|     | 12.6. Debug Operation                                 | 126 |

|     | 12.7. Chip Erase                                      |     |

|     | 12.8. Programming                                     | 127 |

|     | 12.9. Intellectual Property Protection                | 128 |

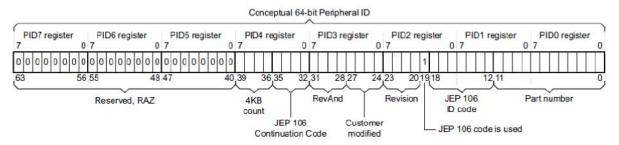

|     | 12.10. Device Identification                          |     |

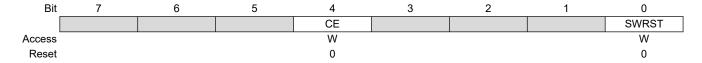

|     | 12.11. Functional Description                         |     |

|     | 12.12. DSU Register Summary                           |     |

|     | 12.13. Register Description                           | 134 |

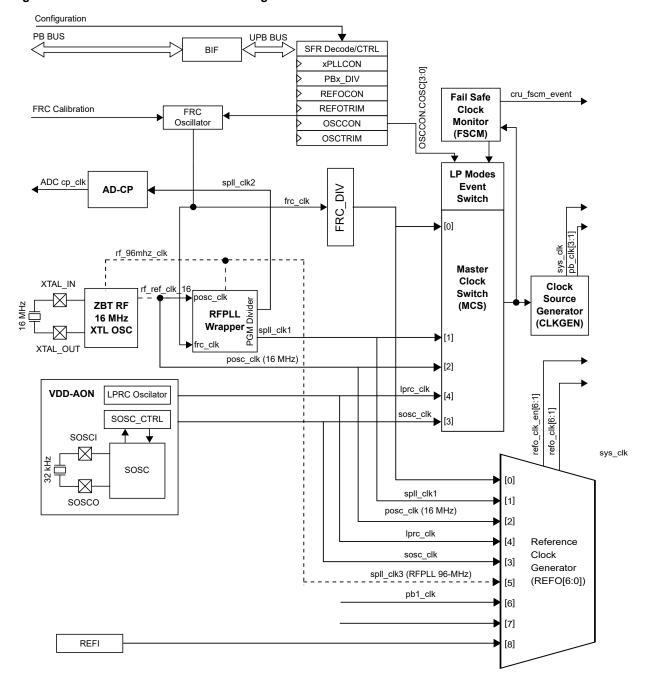

| 13. | Clock and Reset Unit (CRU)                            | 155 |

|     | 13.1. Overview                                        | 155 |

|     | 13.2. Features                                        | 155 |

|     | 13.3. Block Diagram                                   | 156 |

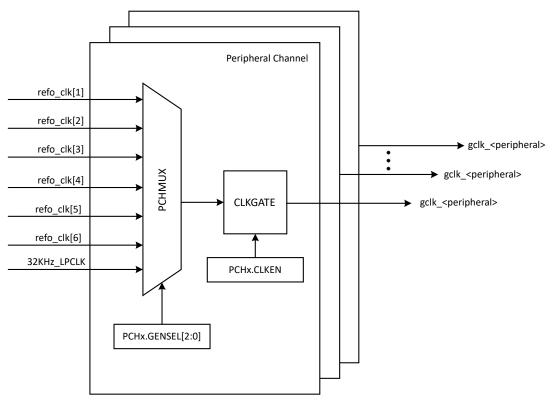

|     | 13.4. System and Peripheral Clock Generation (CLKGEN) | 158 |

|     | 13.5. Idle Mode                                       | 158 |

|     | 13.6. Dream Mode                                      | 158 |

|     | 13.7. FRCDIV                                          | 159 |

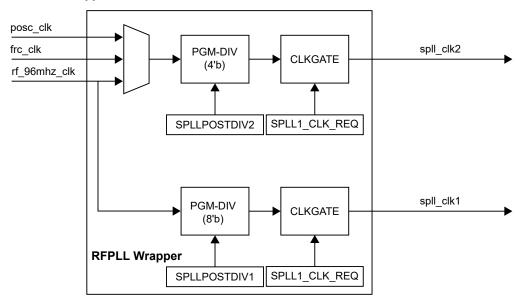

|     | 13.8. RFPLL Wrapper                                   |     |

|     | 13.9. Start-up Considerations                         |     |

|     | 13.10. Fail-Safe Clock Monitor                        |     |

|     | 13.11. Fast RC Oscillator                             |     |

|     | 13.12. Secondary Oscillator                           |     |

|     | 13.13. Low Power RC Oscillator (LPRC)                 |     |

|     | 13.14. Reference Clock Generator                      |     |

|     | 13.15. CRU Configuration Registers                    |     |

|     | 13.16. Register Summary                               |     |

|     | 13.17. Register Description                           |     |

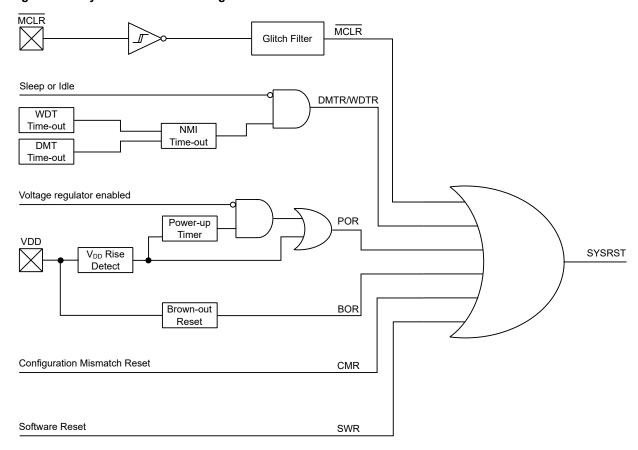

|     | 13.18. Resets                                         | 182 |

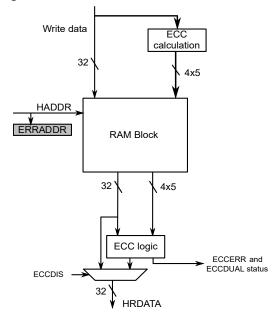

| 14. | RAM Error Correction Code (RAMECC)                    | 197 |

|     | 14.1. Overview                                        | 197 |

|     | 14.2. Features                                        | 197 |

|     | 14.3. Block Diagram                                   | 197 |

|     | 14.4. Signal Description                              | 197 |

|     | 14.5. Product Dependencies                            |     |

|     | 14.6. Functional Description                          |     |

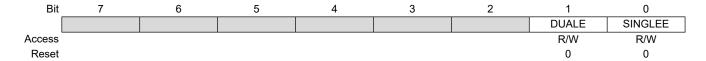

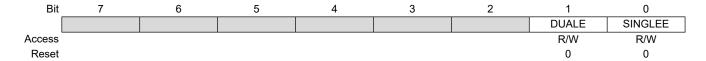

|     | 14.7. Register Summary - RAMECC                       |     |

|     | 14.8. Register Description                            | 200 |

| 15. | Power Management Unit (PMU)                           | 207 |

|     | 15.1. Overview                                        | 207 |

|     | 15.2.  | Power Modes                                      | 207 |

|-----|--------|--------------------------------------------------|-----|

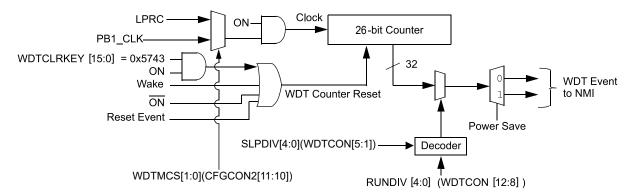

| 16. | Watch  | ndog Timer (WDT)                                 | 209 |

|     | 16.1.  | Overview                                         | 209 |

|     | 16.2.  | Features                                         | 209 |

|     | 16.3.  | Applications                                     | 209 |

|     | 16.4.  | Block Diagram                                    | 211 |

|     | 16.5.  | Configuration                                    | 211 |

|     | 16.6.  | Register Summary - WDT                           | 212 |

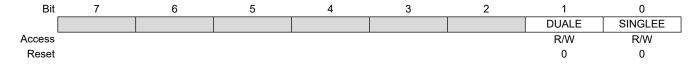

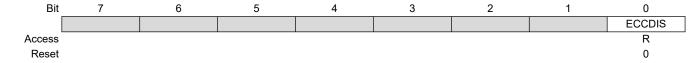

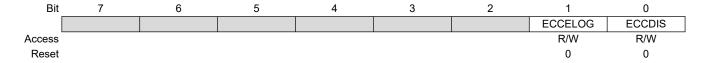

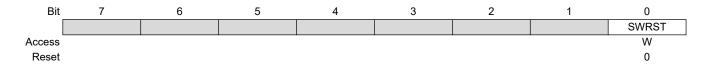

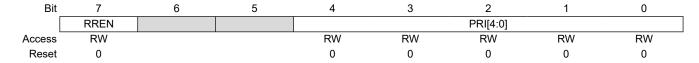

|     | 16.7.  | Register Description                             | 212 |

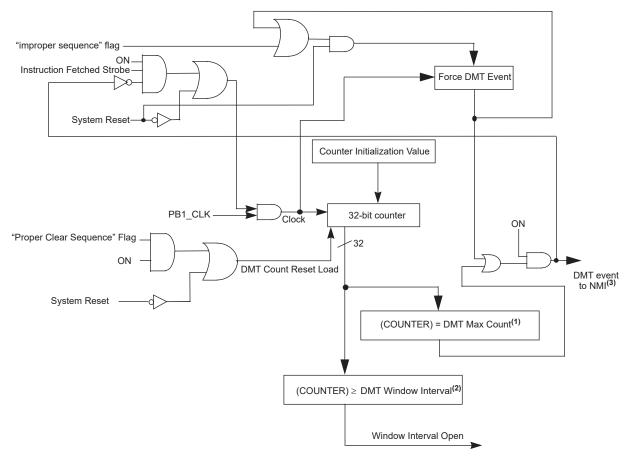

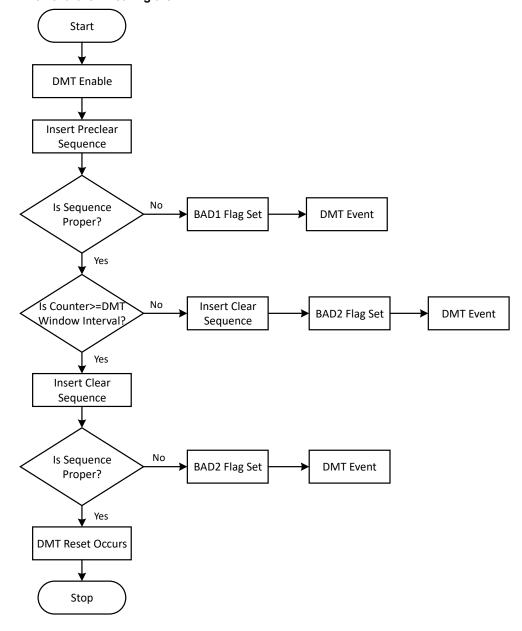

| 17. | Deadı  | man Timer (DMT)                                  | 214 |

|     | 17.1.  | Overview                                         | 214 |

|     | 17.2.  | Features                                         | 214 |

|     | 17.3.  | Block Diagram                                    | 214 |

|     | 17.4.  | DMT Operation                                    | 215 |

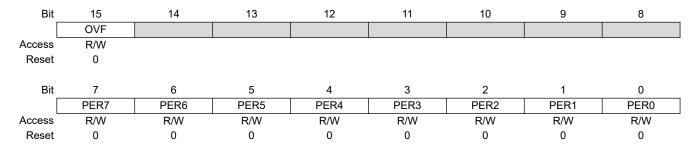

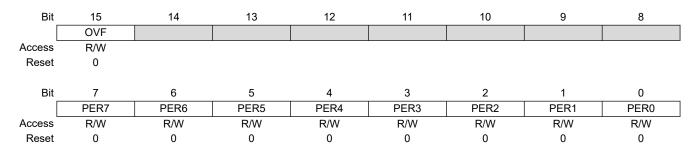

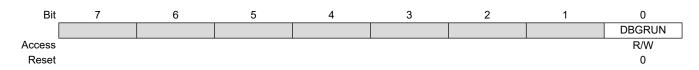

|     | 17.5.  | Register Summary                                 | 218 |

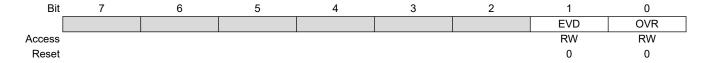

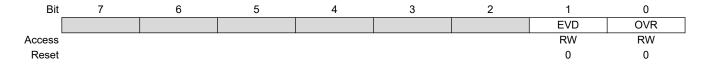

|     | 17.6.  | Register Description                             | 219 |

| 18. | Syste  | m Configuration and Register Locking (CFG)       | 228 |

|     | 18.1.  | Overview                                         | 228 |

|     | 18.2.  | Applications                                     | 229 |

|     | 18.3.  | CFG Register Summary                             | 230 |

|     | 18.4.  | Register Description                             | 231 |

| 19. | Regis  | ter Locking                                      | 263 |

|     | 19.1.  | System Lock Register                             | 263 |

|     | 19.2.  | Register Summary                                 | 265 |

|     | 19.3.  | Register Description                             | 265 |

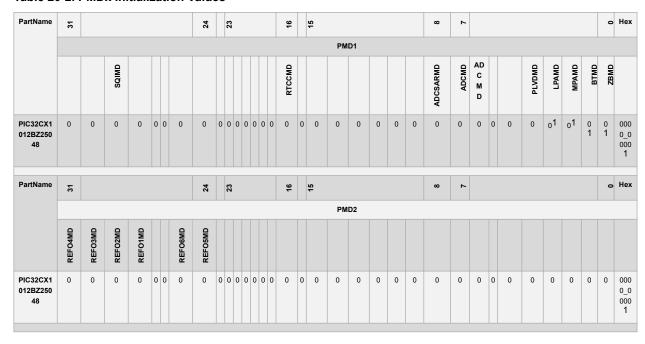

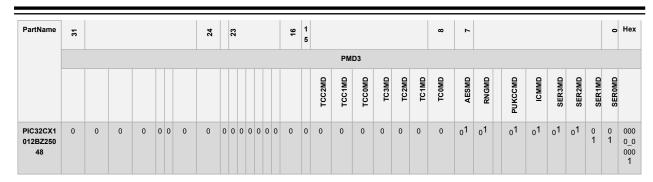

| 20. | Peripl | heral Module Disable Register (PMD)              | 267 |

|     | 20.1.  | Overview                                         | 267 |

|     | 20.2.  | Enabling Peripherals                             | 267 |

|     | 20.3.  | Registers and Bits                               | 267 |

|     | 20.4.  | PMD Register                                     | 267 |

|     | 20.5.  | PMDx Initialization Values by Variant Name       | 271 |

| 21. | Real-  | Time Counter and Calendar (RTCC)                 | 273 |

|     | 21.1.  | Overview                                         | 273 |

|     | 21.2.  | Features                                         | 273 |

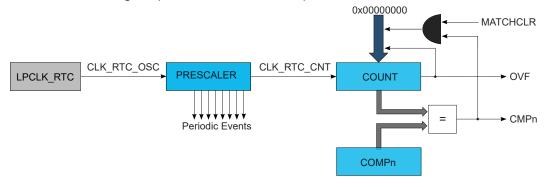

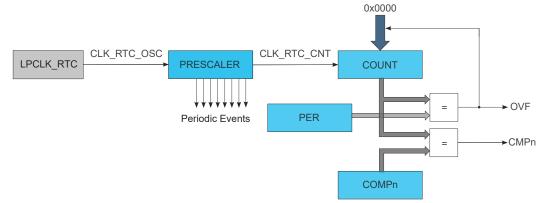

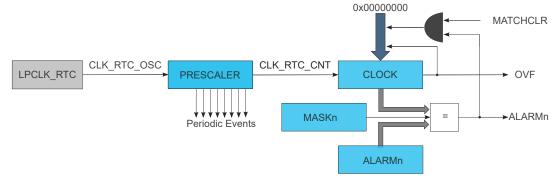

|     | 21.3.  | Block Diagram                                    | 273 |

|     | 21.4.  | Signal Description                               | 274 |

|     | 21.5.  | Product Dependencies                             | 275 |

|     | 21.6.  | Functional Description                           | 276 |

|     | 21.7.  | Register Summary - Mode 0 - 32-Bit Counter       | 286 |

|     | 21.8.  | Register Description - Mode 0 - 32-Bit Counter   | 287 |

|     | 21.9.  | Register Summary - Mode 1 - 16-Bit Counter       | 306 |

|     | 21.10  | . Register Description - Mode 1 - 16-Bit Counter | 307 |

|     | 21.11  | . Register Summary - Mode 2 - Clock/Calendar     | 327 |

|     | 21.12  | Register Description - Mode 2 - Clock/Calendar    | 328 |

|-----|--------|---------------------------------------------------|-----|

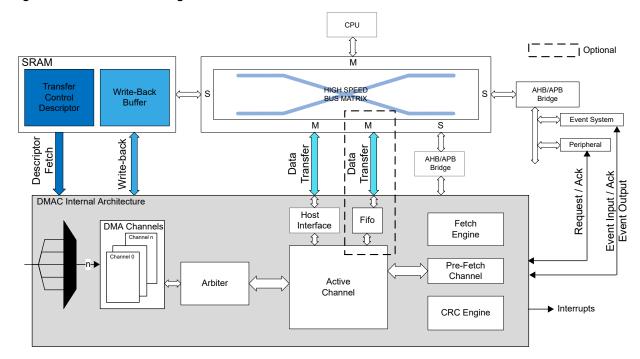

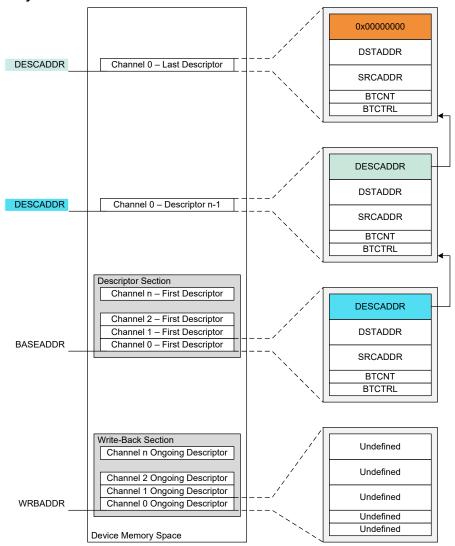

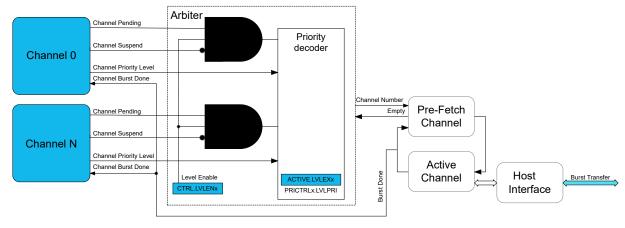

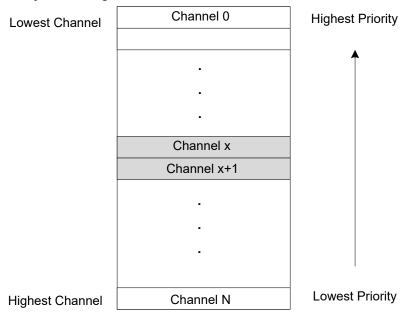

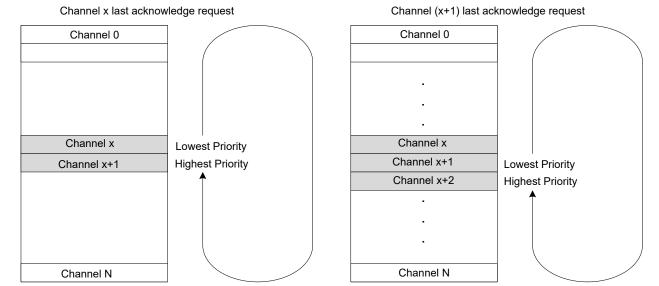

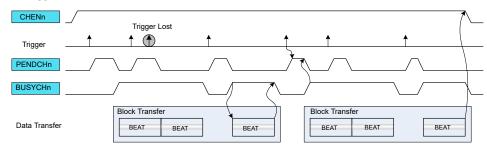

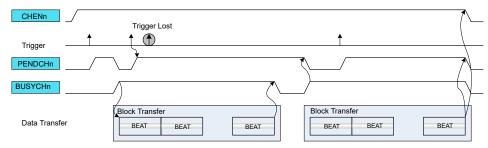

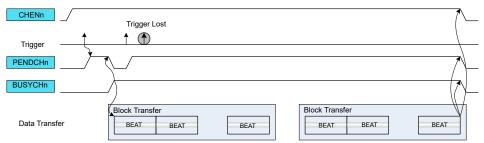

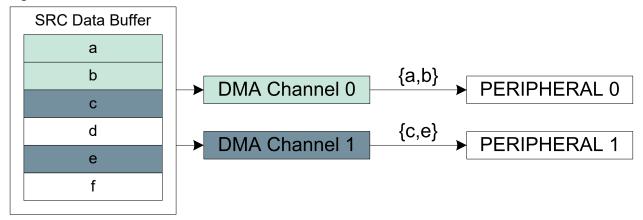

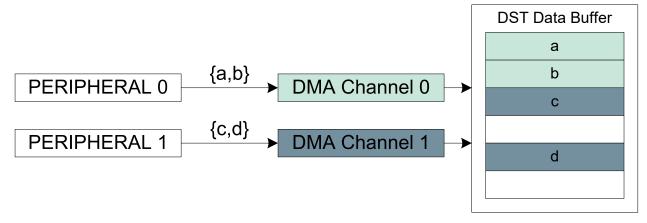

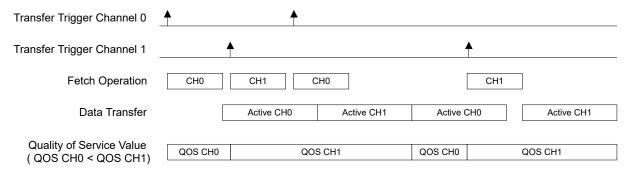

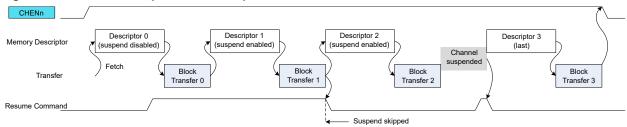

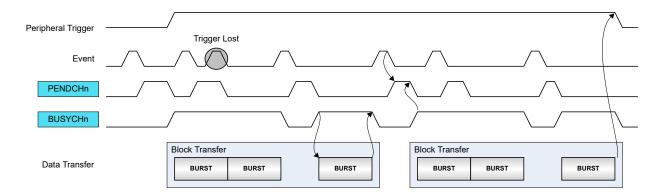

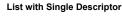

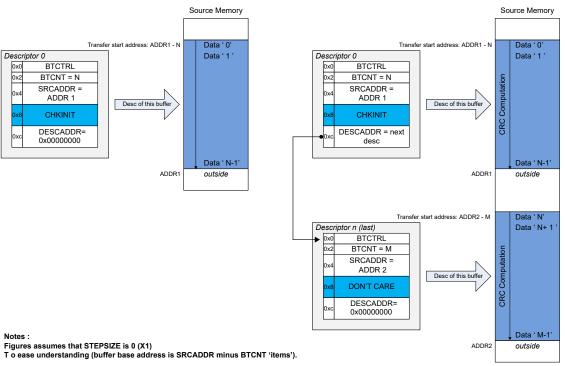

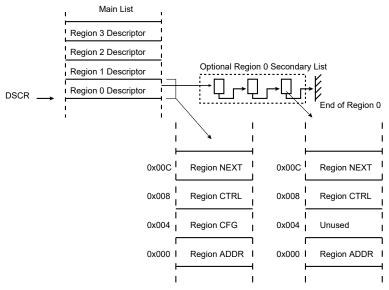

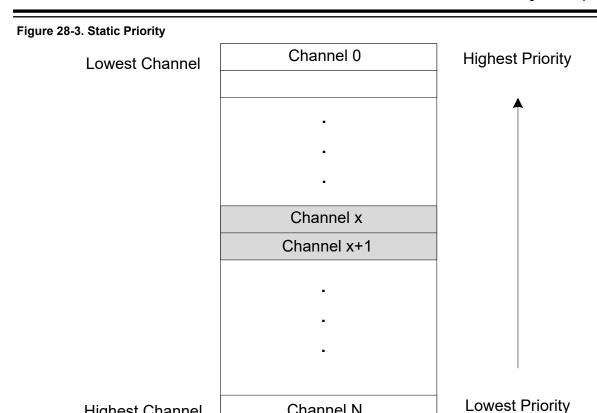

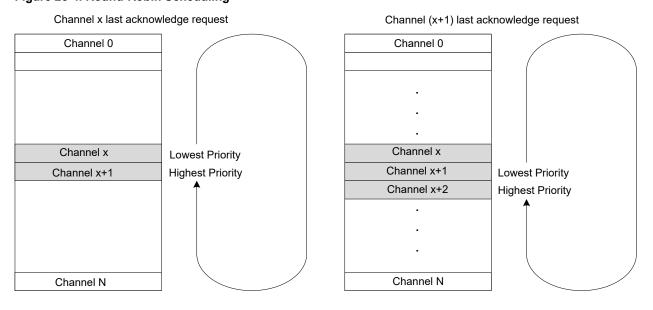

| 22. | Direct | Memory Access Controller (DMAC)                   | 347 |

|     | 22.1.  | Overview                                          | 347 |

|     | 22.2.  | Features                                          | 347 |

|     | 22.3.  | Block Diagram                                     | 349 |

|     | 22.4.  | Signal Description                                | 349 |

|     | 22.5.  | Product Dependencies                              | 349 |

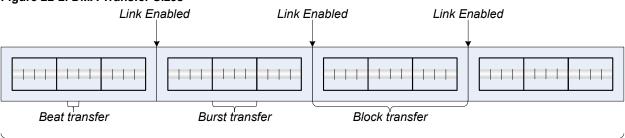

|     | 22.6.  | Functional Description                            | 350 |

|     | 22.7.  | DMAC Register Summary                             | 373 |

|     | 22.8.  | Register Description                              | 378 |

|     | 22.9.  | DMAC Register Summary (SRAM)                      | 406 |

|     | 22.10  | Register Description - SRAM                       | 406 |

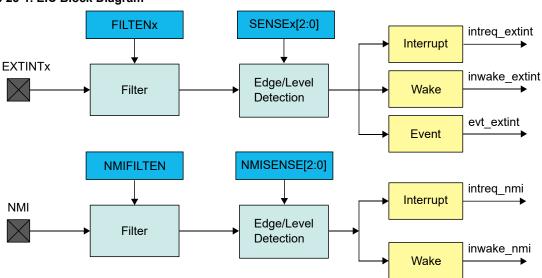

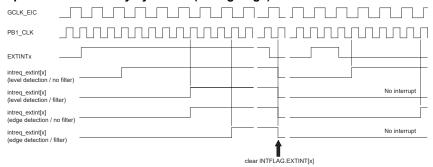

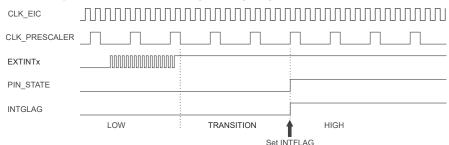

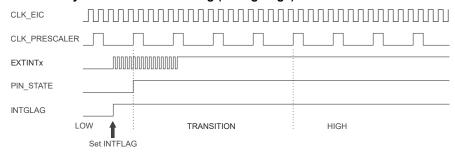

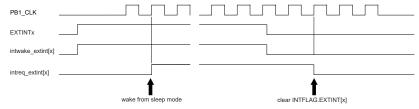

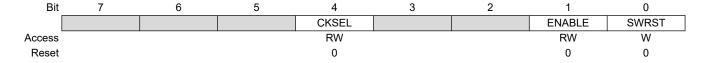

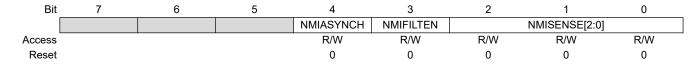

| 23. | Exterr | nal Interrupt Controller (EIC)                    | 413 |

|     | 23.1.  | Overview                                          | 413 |

|     | 23.2.  | Features                                          | 413 |

|     | 23.3.  | Block Diagram                                     | 413 |

|     | 23.4.  | Signal Description                                | 413 |

|     | 23.5.  | Product Dependencies.                             | 414 |

|     | 23.6.  | Functional Description                            | 415 |

|     | 23.7.  | EIC Register Summary                              | 421 |

|     | 23.8.  | Register Description.                             | 421 |

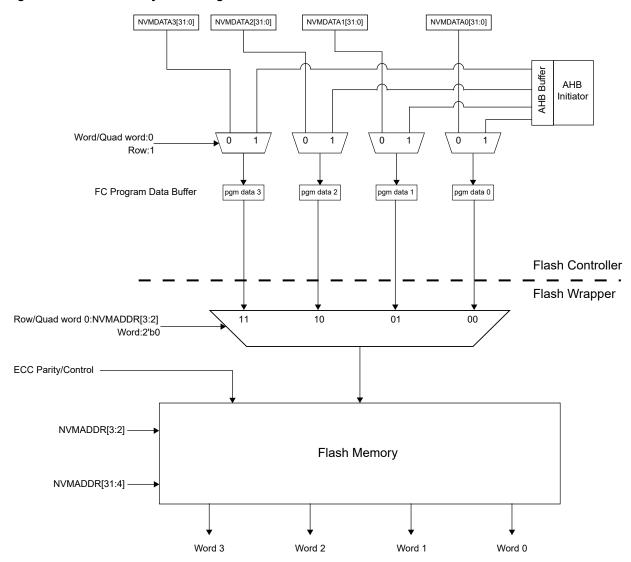

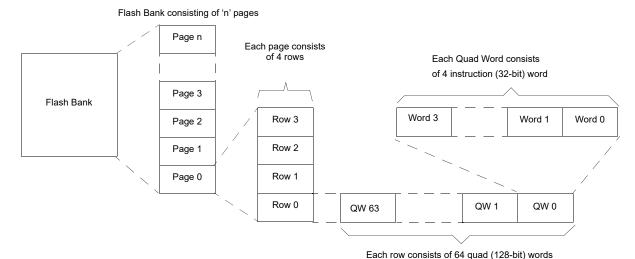

| 24. | Flash  | Memory                                            | 436 |

|     | 24.1.  | Overview                                          | 436 |

|     | 24.2.  | Features                                          | 436 |

|     |        | Functional Block Diagram                          |     |

|     |        | Flash Memory Addressing                           |     |

|     |        | Memory Configuration                              |     |

|     |        | Boot Flash Memory (BFM) Partitions                |     |

|     |        | Program Flash Memory (PFM) Partitions             |     |

|     |        | Error Correcting Code (ECC) and Flash Programming |     |

|     |        | Interrupts                                        |     |

|     | 24.10  | Error Detection                                   | 440 |

|     |        | NVMKEY Register Unlocking Sequence                |     |

|     |        | Word Programming                                  |     |

|     |        | Quad Word Programming                             |     |

|     |        | Row Programming                                   |     |

|     |        | Page Erase                                        |     |

|     |        | Program Flash Memory (PFM) Erase                  |     |

|     |        | Pre-Program                                       |     |

|     |        | Device Code Protection bit (CP)                   |     |

|     |        | Operation in Power-Saving Modes                   |     |

|     |        | Operation in Debug Mode                           |     |

|     |        | Effects of Various Resets                         |     |

|     |        | Control Registers                                 |     |

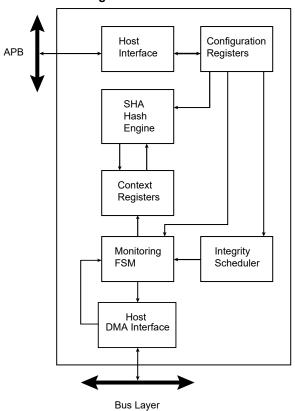

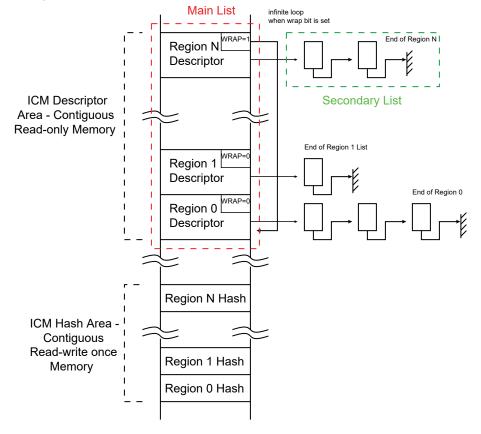

| 25. | Integr | ity Check Monitor (ICM)                           | 467 |

|     | 25.1.  | Overview                                                                | 467 |

|-----|--------|-------------------------------------------------------------------------|-----|

|     | 25.2.  | Features                                                                | 467 |

|     | 25.3.  | Block Diagram                                                           | 468 |

|     | 25.4.  | Signal Description                                                      | 468 |

|     | 25.5.  | Product Dependencies                                                    | 468 |

|     | 25.6.  | Functional Description                                                  | 469 |

|     | 25.7.  | Register Summary - ICM                                                  | 481 |

|     | 25.8.  | Register Description                                                    | 482 |

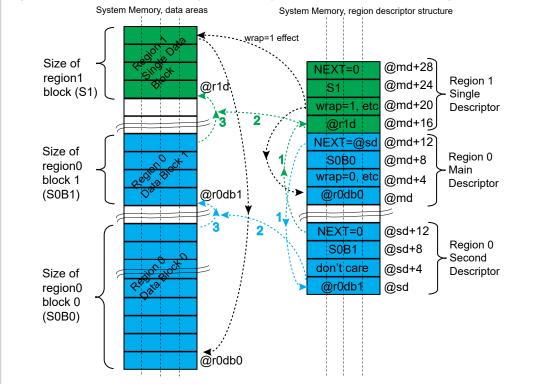

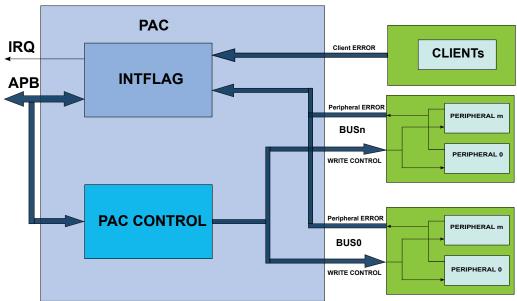

| 26. | Periph | eral Access Controller (PAC)                                            | 500 |

|     | 26.1.  | Overview                                                                | 500 |

|     | 26.2.  | Features                                                                | 500 |

|     | 26.3.  | Block Diagram                                                           | 500 |

|     | 26.4.  | Product Dependencies                                                    | 500 |

|     | 26.5.  | Functional Description                                                  | 501 |

|     | 26.6.  | Register Summary                                                        | 504 |

|     | 26.7.  | Register Description                                                    | 504 |

| 27. | Frequ  | ency Meter (FREQM)                                                      | 519 |

|     | 27.1.  | Overview                                                                | 519 |

|     | 27.2.  | Features                                                                | 519 |

|     | 27.3.  | Block Diagram                                                           | 519 |

|     | 27.4.  | Signal Description                                                      | 519 |

|     | 27.5.  | Product Dependencies                                                    | 519 |

|     | 27.6.  | Functional Description                                                  | 520 |

|     | 27.7.  | Register Summary - FREQM                                                | 523 |

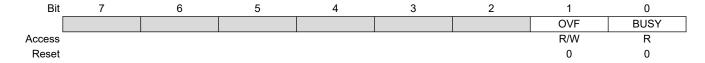

|     | 27.8.  | Register Description                                                    | 523 |

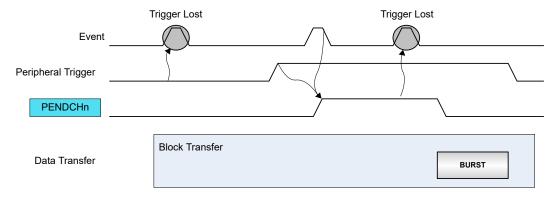

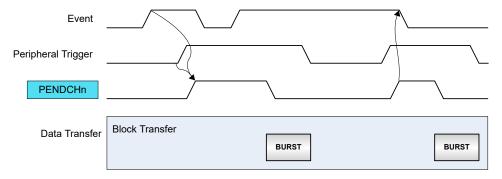

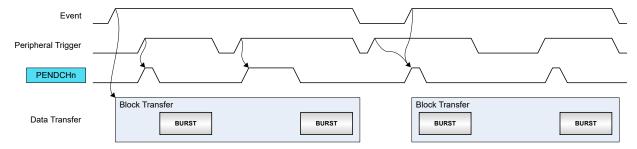

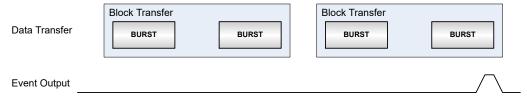

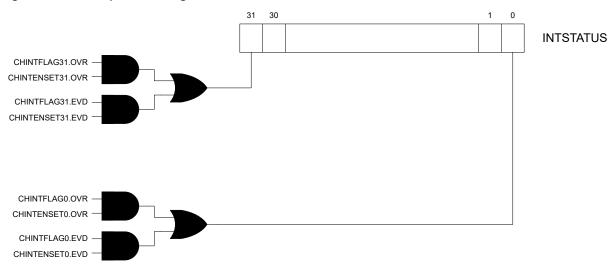

| 28. | Event  | System (EVSYS)                                                          | 533 |

|     | 28.1.  | Overview                                                                | 533 |

|     | 28.2.  | Features                                                                | 533 |

|     |        | Block Diagram                                                           |     |

|     |        | Product Dependencies                                                    |     |

|     |        | Functional Description                                                  |     |

|     |        | Register Summary                                                        |     |

|     |        | Register Description                                                    |     |

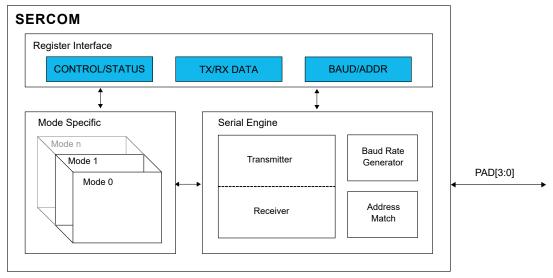

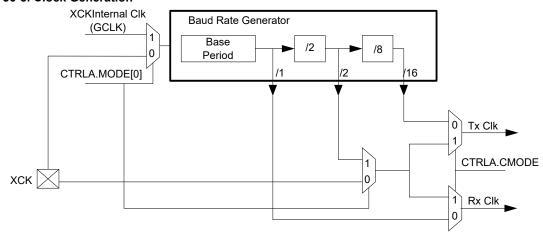

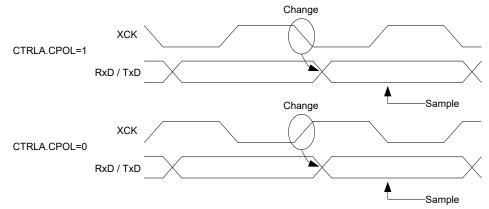

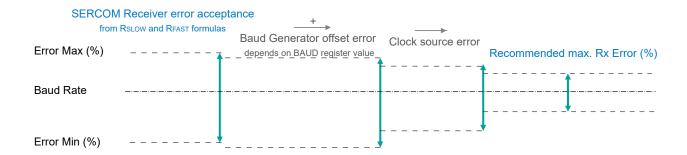

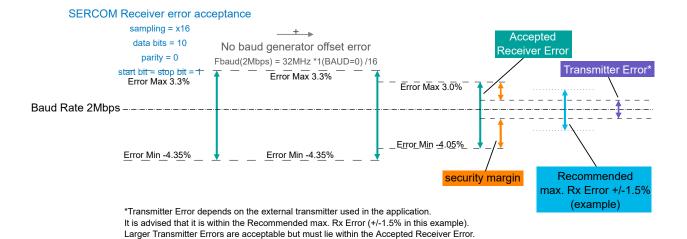

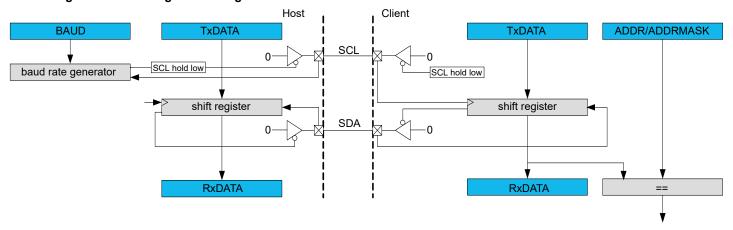

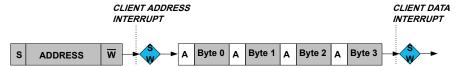

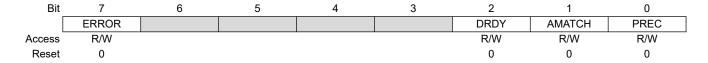

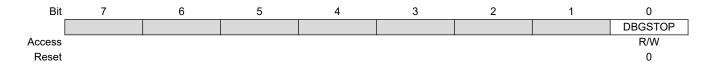

| 29. | Serial | Communication Interface (SERCOM)                                        | 560 |

|     | 29.1.  | Overview                                                                | 560 |

|     |        | Features                                                                |     |

|     |        | Block Diagram                                                           |     |

|     |        | Signal Description                                                      |     |

|     |        | Product Dependencies                                                    |     |

|     |        | Functional Description                                                  |     |

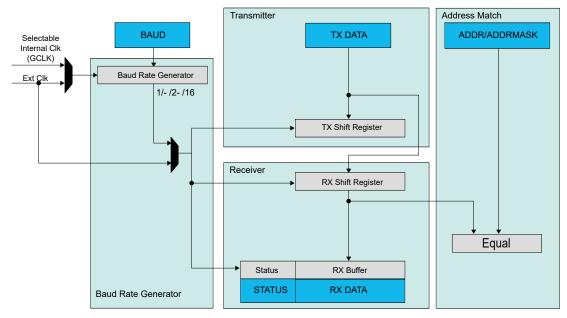

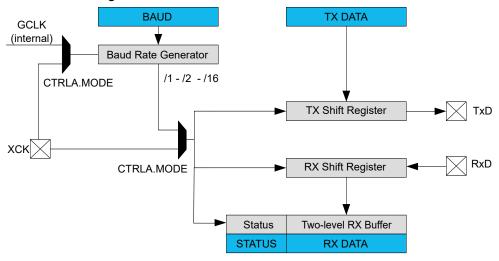

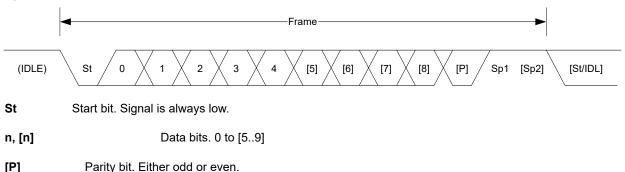

| 30. | SERC   | OM Synchronous and Asynchronous Receiver and Transmitter (SERCOM USART) | 566 |

|     |        | Overview                                                                |     |

|     |        | USART Features                                                          |     |

|     |        | Block Diagram                                                           |     |

|     |        |                                                                         |     |

|     | 30.4.  | Signal Description                                     | 567 |

|-----|--------|--------------------------------------------------------|-----|

|     | 30.5.  | Product Dependencies                                   | 567 |

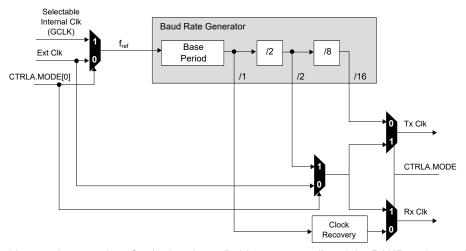

|     | 30.6.  | Functional Description                                 | 569 |

|     | 30.7.  | Register Summary                                       | 582 |

|     | 30.8.  | Register Description                                   | 582 |

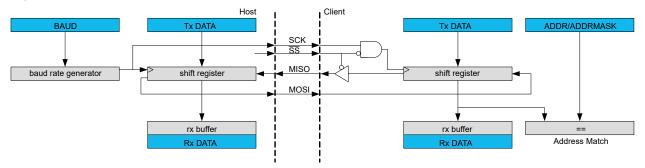

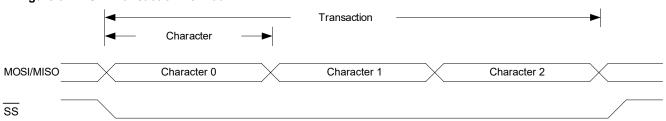

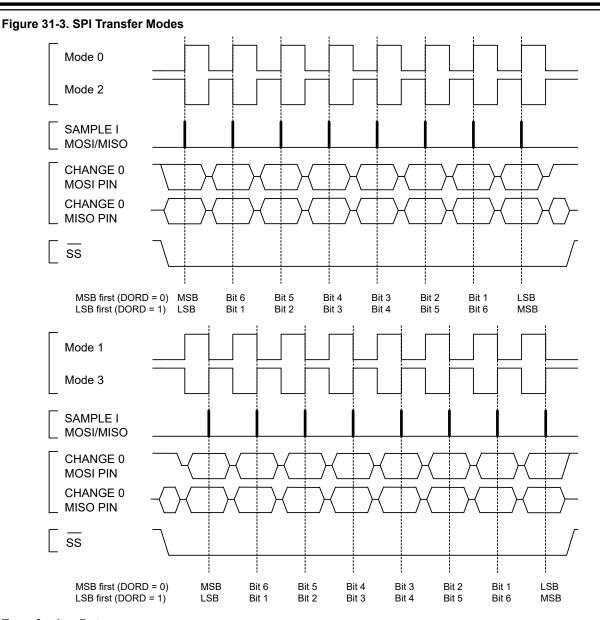

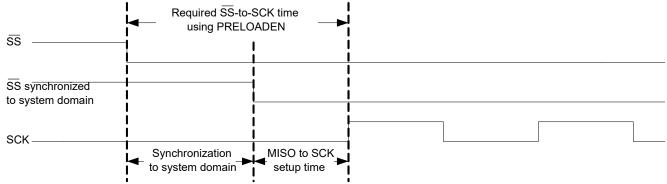

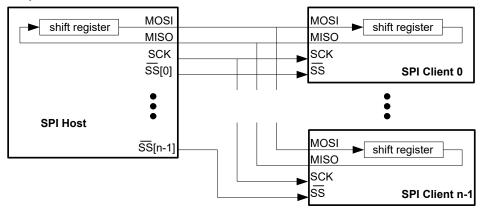

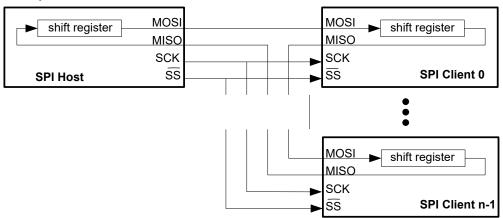

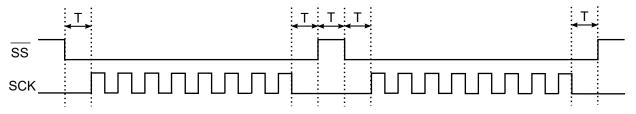

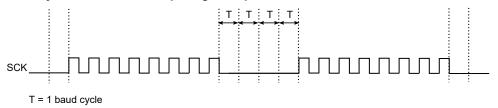

| 31. | SERC   | COM Serial Peripheral Interface (SERCOM SPI)           | 601 |

|     | 31.1.  | Overview                                               | 601 |

|     | 31.2.  | Features                                               | 601 |

|     | 31.3.  | Block Diagram                                          | 601 |

|     | 31.4.  | Signal Description                                     | 602 |

|     | 31.5.  | Product Dependencies                                   | 602 |

|     | 31.6.  | Functional Description                                 | 603 |

|     | 31.7.  | Register Summary                                       | 613 |

|     | 31.8.  | Register Description                                   | 613 |

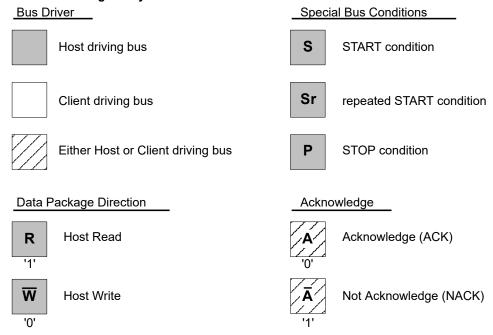

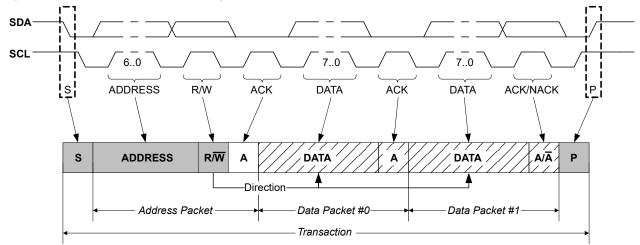

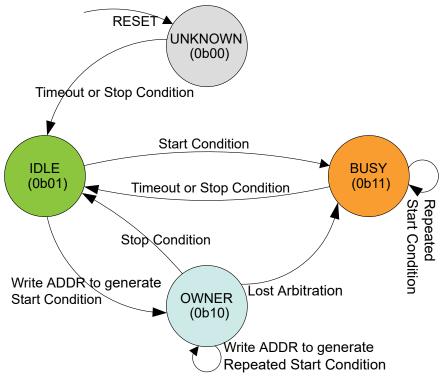

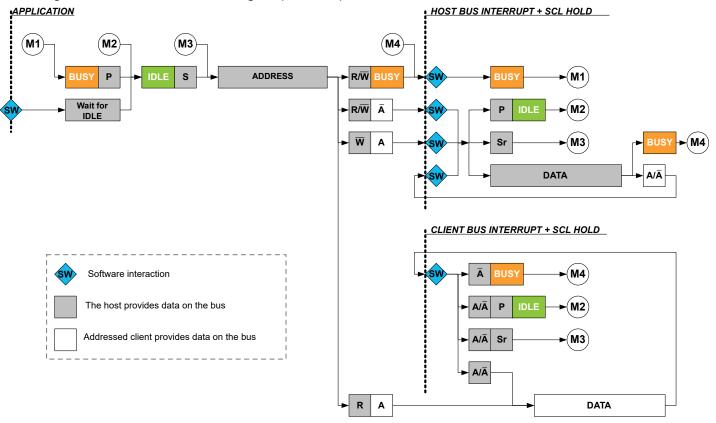

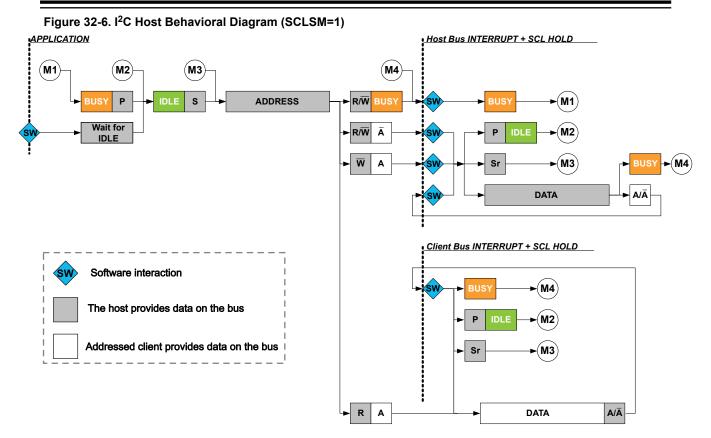

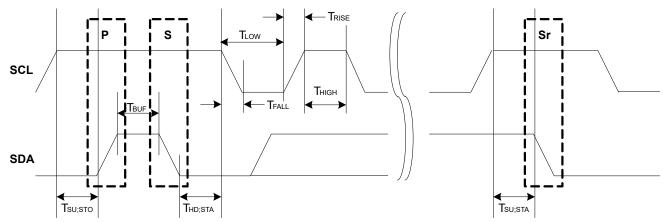

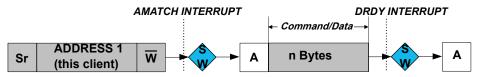

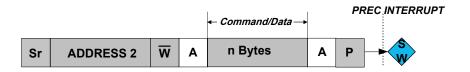

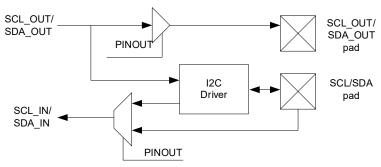

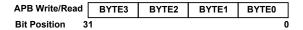

| 32. | SERC   | COM Inter-Integrated Circuit (SERCOM I <sup>2</sup> C) | 629 |

|     | 32.1.  | Overview                                               | 629 |

|     | 32.2.  | Features                                               | 629 |

|     | 32.3.  | Block Diagram                                          | 630 |

|     | 32.4.  | Signal Description                                     | 630 |

|     | 32.5.  | Product Dependencies                                   | 630 |

|     | 32.6.  | Functional Description                                 | 631 |

|     | 32.7.  | Register Summary - I2C Client                          | 648 |

|     |        | Register Description - I <sup>2</sup> C Client         |     |

|     |        | Register Summary - I2C Host                            |     |

|     | 32.10  | Register Description – I <sup>2</sup> C Host           | 662 |

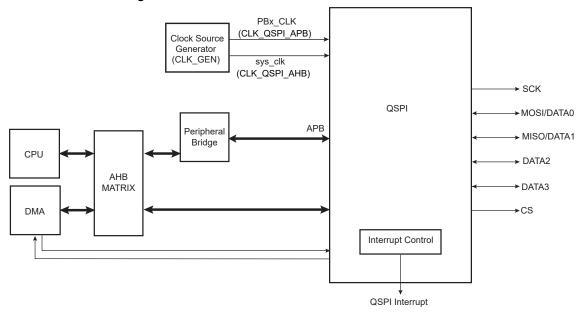

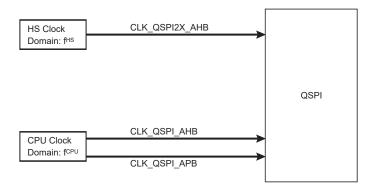

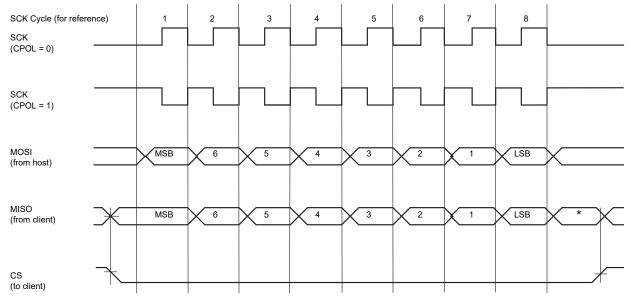

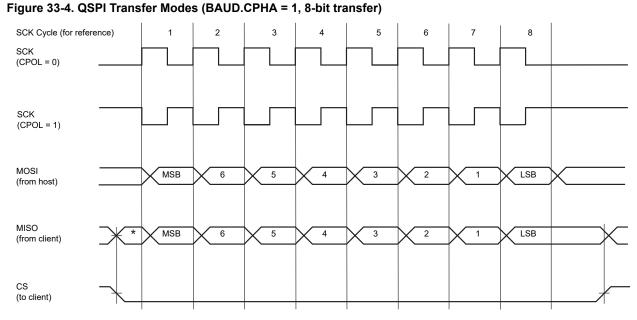

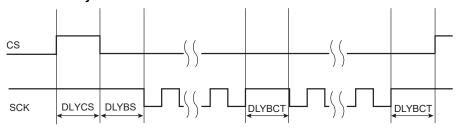

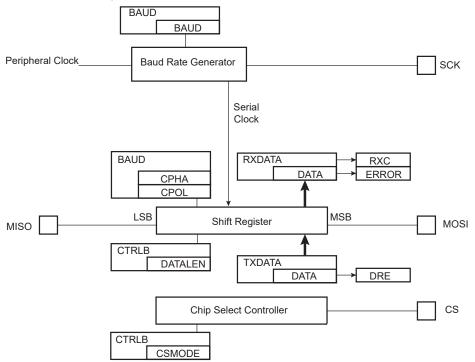

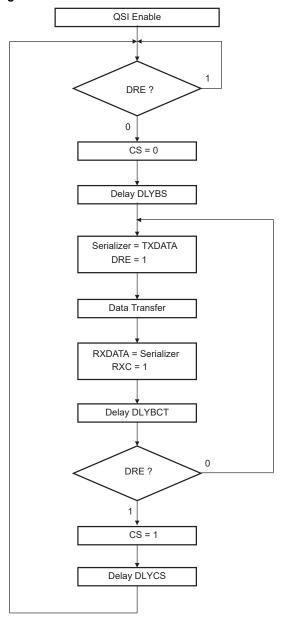

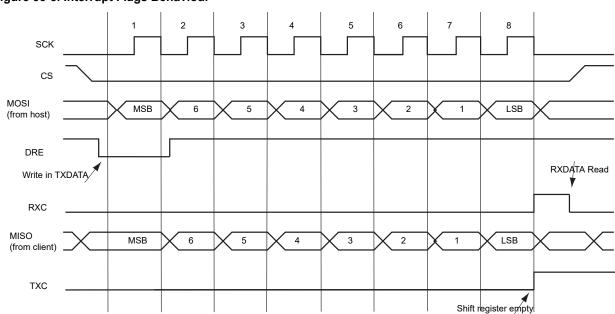

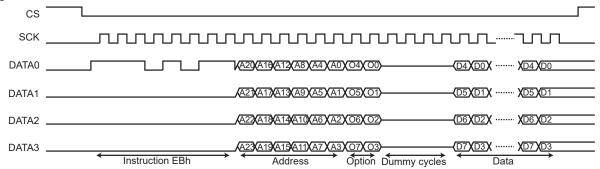

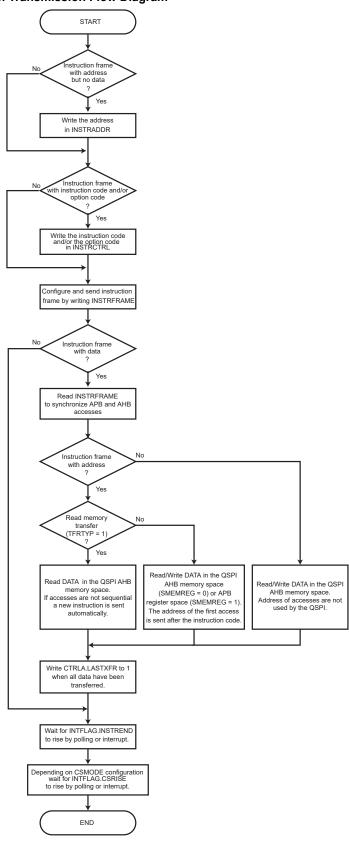

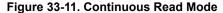

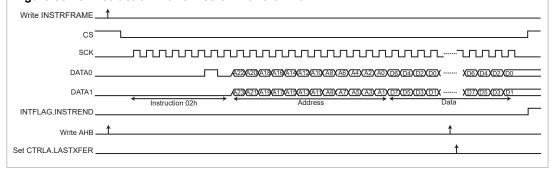

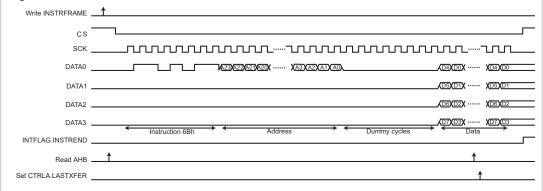

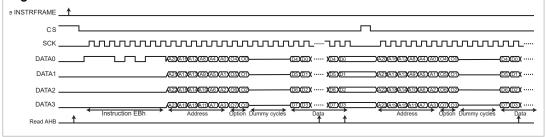

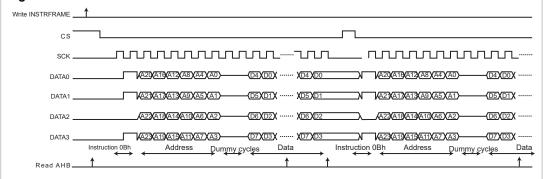

| 33. |        | Serial Peripheral Interface (QSPI)                     |     |

|     | 33.1.  | Overview                                               | 679 |

|     | 33.2.  | Features                                               | 679 |

|     | 33.3.  | Block Diagram                                          | 680 |

|     | 33.4.  | Signal Description                                     | 680 |

|     |        | Product Dependencies                                   |     |

|     |        | Functional Description                                 |     |

|     |        | Register Summary                                       |     |

|     | 33.8.  | Register Description                                   | 699 |

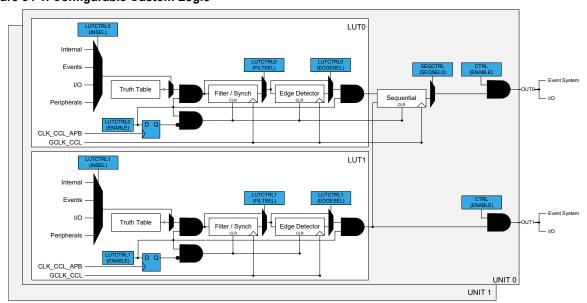

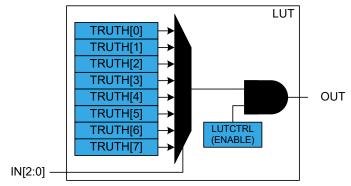

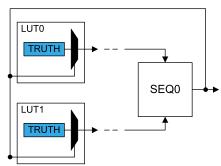

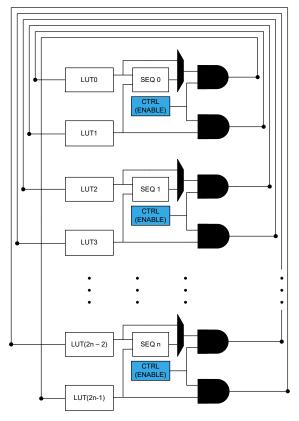

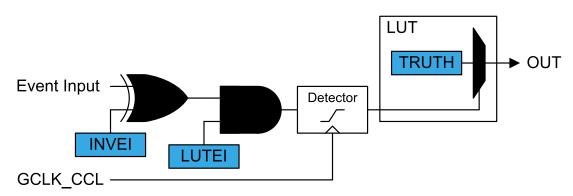

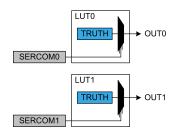

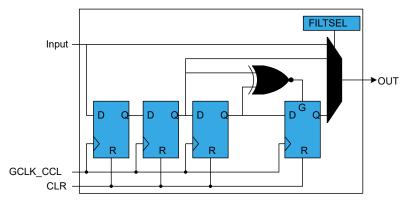

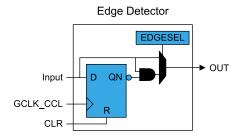

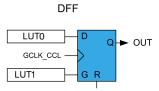

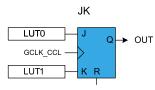

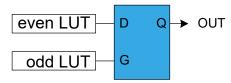

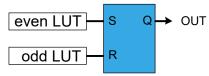

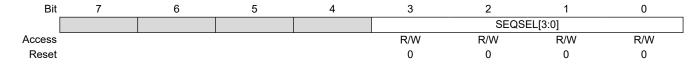

| 34. | Confi  | gurable Custom Logic (CCL)                             | 720 |

|     |        | Overview                                               |     |

|     | 34.2.  | Features                                               | 720 |

|     | 34.3.  | Block Diagram                                          | 720 |

|     |        | Signal Description                                     |     |

|     |        | Product Dependencies                                   |     |

|     |        | Functional Description                                 |     |

|     |        | Register Summary                                       |     |

|     | 34.8.  | Register Description                                   | 731 |

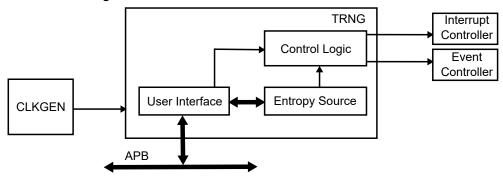

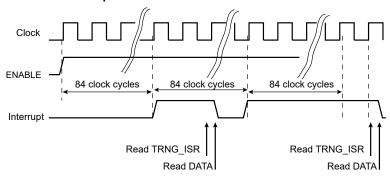

| 35. | True I | Random Number Generator (TRNG)                         | 736 |

|     | 35.1.  | Overview                            | . 736 |

|-----|--------|-------------------------------------|-------|

|     | 35.2.  | Features                            | . 736 |

|     | 35.3.  | Block Diagram                       | 736   |

|     | 35.4.  | Signal Description                  | . 736 |

|     | 35.5.  | Product Dependencies                | 736   |

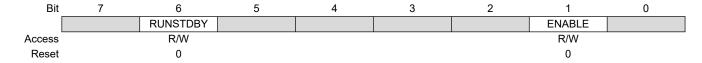

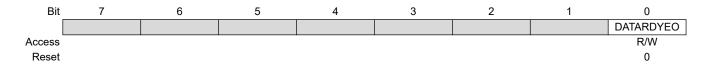

|     | 35.6.  | Functional Description              | 737   |

|     | 35.7.  | Register Summary                    | 740   |

|     | 35.8.  | Register Description                | 740   |

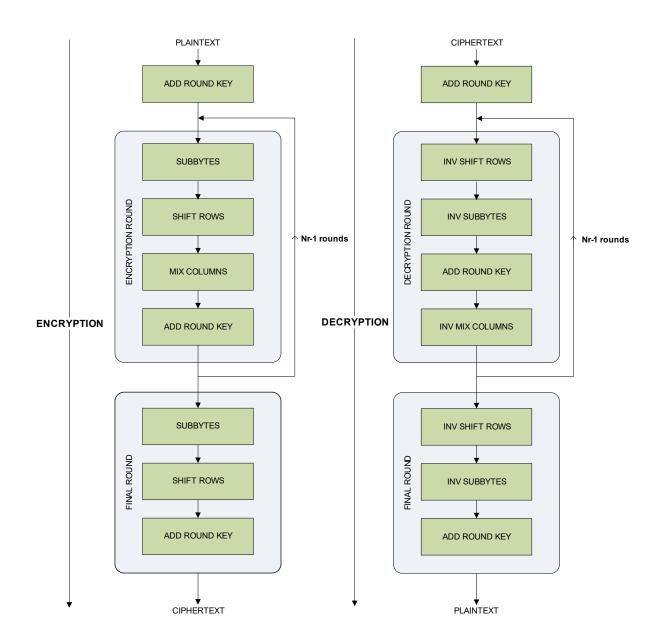

| 36. | Advar  | ced Encryption Standard (AES)       | . 747 |

|     | 36.1.  | Overview                            | . 747 |

|     | 36.2.  | Features                            | . 747 |

|     | 36.3.  | Block Diagram                       | 748   |

|     | 36.4.  | Signal Description                  | . 749 |

|     | 36.5.  | Product Dependencies                | 749   |

|     | 36.6.  | Functional Description              | 750   |

|     | 36.7.  | Register Summary                    | 758   |

|     | 36.8.  | Register Description                | . 760 |

| 37. | Public | Key Cryptography Controller (PUKCC) | . 776 |

|     | 37.1.  | Overview                            | . 776 |

|     | 37.2.  | Product Dependencies                | 776   |

|     |        | Functional Description              |       |

| 38. | Analo  | g-to-Digital Converter (ADC)        | 888   |

|     | 38.1.  | Overview                            | . 888 |

|     |        | ADC Operation                       |       |

|     |        | ADC Module Configuration            |       |

|     |        | Additional ADC Functions            |       |

|     |        | Interrupts                          |       |

|     |        | Power-Saving Modes of Operation     |       |

|     |        | Effects of Reset                    |       |

|     |        | Transfer Function                   |       |

|     |        | ADC Sampling Requirements           |       |

|     |        | Connection Considerations           |       |

|     |        | Register Description                |       |

| 39. | Analo  | g Comparators (AC)                  | 957   |

|     |        | Overview                            |       |

|     |        | Features                            |       |

|     |        | Block Diagram                       |       |

|     |        | Product Dependencies                |       |

|     |        | Functional Description              |       |

|     |        | Register Summary                    |       |

|     |        | Register Description                |       |

|     |        |                                     |       |

| 40. | Timer  | Counter (TC)                        | . 984 |

|     | 40.1.  | Overview                            | . 984 |

|     | 40.2.  | Features                            | . 984 |

|     | 40.3.  | Block Diagram                                                             | 985  |

|-----|--------|---------------------------------------------------------------------------|------|

|     | 40.4.  | Signal Description                                                        | 985  |

|     | 40.5.  | Product Dependencies                                                      | 986  |

|     | 40.6.  | Functional Description                                                    | 987  |

|     | 40.7.  | Register Description                                                      | 1001 |

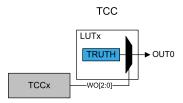

| 41. | Timer  | /Counter for Control Applications (TCC)                                   | 1060 |

|     | 41.1.  | Overview                                                                  | 1060 |

|     | 41.2.  | Features                                                                  | 1060 |

|     | 41.3.  | Block Diagram                                                             | 1061 |

|     | 41.4.  | Signal Description                                                        | 1061 |

|     | 41.5.  | Product Dependencies                                                      | 1061 |

|     | 41.6.  | Functional Description                                                    | 1062 |

|     | 41.7.  | Register Summary                                                          | 1091 |

|     | 41.8.  | Register Description                                                      | 1092 |

| 42. | Zigbe  | e Bluetooth Radio Subsystem (ZBT)                                         | 1125 |

|     | 42.1.  | Overview                                                                  | 1125 |

|     | 42.2.  | Features                                                                  | 1125 |

|     | 42.3.  | Wireless Subsystem Top Level Diagram                                      | 1127 |

|     | 42.4.  | Bluetooth Link Controller                                                 | 1128 |

|     | 42.5.  | Zigbee/Proprietary Data Rate Link Controller                              | 1129 |

|     | 42.6.  | Radio Arbiter                                                             | 1130 |

|     | 42.7.  | RF Physical Layer                                                         | 1130 |

|     | 42.8.  | Frequency Synthesizer                                                     | 1130 |

|     | 42.9.  | RFLDO                                                                     | 1131 |

| 43. | Electr | ical Characteristics                                                      | 1132 |

|     | 43.1.  | Absolute Maximum Electrical Characteristics                               | 1132 |

|     | 43.2.  | DC Electrical Characteristics                                             | 1132 |

|     | 43.3.  | Thermal Specifications                                                    | 1133 |

|     | 43.4.  | Active Current Consumption DC Electrical Specifications                   | 1133 |

|     | 43.5.  | Idle Current Consumption DC Electrical Specifications                     | 1135 |

|     | 43.6.  | Sleep Current Consumption DC Electrical Specifications                    | 1137 |

|     | 43.7.  | Deep Sleep Current Consumption DC Electrical Specifications               | 1139 |

|     | 43.8.  | XDS (Extreme Deep Sleep) Current Consumption DC Electrical Specifications | 1140 |

|     | 43.9.  | External XTAL and Clock AC Electrical Specifications                      | 1141 |

|     | 43.10  | XOSC32 AC Electrical Specifications                                       | 1143 |

|     | 43.11. | Low Power Internal 32 kHz RC Oscillator AC Electrical Specifications      | 1145 |

|     | 43.12  | FRC AC Electrical Specifications                                          | 1146 |

|     | 43.13  | . Frequency AC Electrical Specifications                                  | 1146 |

|     | 43.14  | . QSPI Module Electrical Specifications                                   | 1147 |

|     | 43.15  | . Power Supply DC Module Electrical Specifications                        | 1148 |

|     | 43.16  | . I/O PIN AC/DC Electrical Specifications                                 | 1154 |

|     | 43.17  | . I <sup>2</sup> C Module Electrical Specifications                       | 1156 |

|     | 43.18  | SPI Module Electrical Specifications                                      | 1161 |

|     |        | ADC Electrical Specifications                                             |      |

|     | 43.20  | Bluetooth Low Energy RF Characteristics                                   | 1167 |

|     | 43.21. Zigbee RF Characteristics            | 1179 |

|-----|---------------------------------------------|------|

| 44. | Packaging Information                       | 1189 |

|     | 44.1. PIC32CX-BZ2 SoC Packaging Information | 1190 |

|     | 44.2. WBZ451 Module Packaging Information   |      |

|     | 44.3. WBZ450 Module Packaging Information   |      |

| 45. | Appendix A: Regulatory Approval             | 1198 |

|     | 45.1. United States                         | 1198 |

|     | 45.2. Canada                                | 1199 |

|     | 45.3. Europe                                | 1201 |

|     | 45.4. Japan                                 | 1202 |

|     | 45.5. Korea                                 | 1202 |

|     | 45.6. Taiwan                                | 1203 |

|     | 45.7. Other Regulatory Information          | 1203 |

| 46. | Document Revision History                   | 1204 |

| Mic | rochip Information                          | 1205 |

|     | The Microchip Website                       | 1205 |

|     | Product Change Notification Service         | 1205 |

|     | Customer Support                            |      |

|     | Microchip Devices Code Protection Feature   | 1205 |

|     | Legal Notice                                | 1205 |

|     | Trademarks                                  |      |

|     | Quality Management System                   | 1207 |

|     | Worldwide Sales and Service                 | 1208 |

### 1. Ordering Information

This chapter provides the ordering information of the PIC32CX-BZ2 and WBZ45 family of devices.

### 1.1 PIC32CXBZ2 SoC and WBZ45 Module Ordering Information

The following table describes the ordering information of the WBZ45 Module.

Table 1-1. WBZ45 Module Ordering Details

| Model No. | Module SoC                   | Description                                            | Regulatory<br>Certification | Ordering Code |

|-----------|------------------------------|--------------------------------------------------------|-----------------------------|---------------|

| WBZ451PE  | PIC32CX1012BZ250<br>48-I/MYX | WBZ451 module with PCB antenna                         | FCC, ISED, CE               | WBZ451PE-I    |

| WBZ451UE  |                              | WBZ451 module with U.FL connector for external antenna | FCC, ISED, CE               | WBZ451UE-I    |

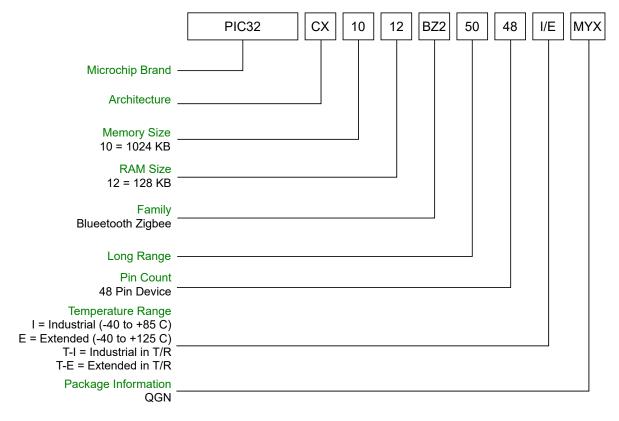

The following figure illustrates the details of the PIC32CXBZ2 ordering information.

Figure 1-1. PIC32CXBZ2 Ordering Information

## 2. Configuration Summary

Table 2-1. PIC32CX-BZ2 and WBZ45 Family Features

|                    |                     |                  |      | Peripherals |        |                    |                     |      |              |     |         |     |     |                       | Analog                  |                          |           |                               | Sec            | Security           |     |      | Wireless                        |                         |                    |               |                     |   |   |   |   |   |   |   |   |

|--------------------|---------------------|------------------|------|-------------|--------|--------------------|---------------------|------|--------------|-----|---------|-----|-----|-----------------------|-------------------------|--------------------------|-----------|-------------------------------|----------------|--------------------|-----|------|---------------------------------|-------------------------|--------------------|---------------|---------------------|---|---|---|---|---|---|---|---|

| Device             | Program Memory (KB) | Data Memory (KB) | Pins | Package     | SERCOM | Timer/Counter (TC) | TCC (24-bit/16-bit) | QSPI | DMA Channels | RTC | ССГ/ГПТ | WDT | DMT | Frequency Measurement | Event System (Channels) | External Interrupt Lines | GPIO Pins | Analog Comparators (Channels) | ADC (Channels) | Temperature Sensor | AES | TRNG | Public Key Cryptography (PUKCC) | Integrity Check Monitor | Max TX Power (dBm) | Bluetooth 5.2 | 802.15.4/Zigbee 3.0 |   |   |   |   |   |   |   |   |

| PIC32CX1012BZ25048 |                     |                  | 48   | QFN         | 4      |                    |                     |      |              |     |         |     |     |                       |                         |                          | 29        | 2                             | 8              |                    |     |      |                                 |                         | 12                 |               |                     |   |   |   |   |   |   |   |   |

| PIC32CX1012BZ24032 | 4004                | 1024             | 1024 | 1024        | 1024   | 1024               | 1024                | 1024 | 1024 128     | 128 | 32      | QFN | 2   | 4                     | 2/1                     | Y                        | 16        | 3 Y                           | 1/2            | Y                  | Υ   | Υ    | 32                              | 4                       | 16                 | 1             | 6                   | Y | Υ | Y | Υ | Υ | 4 | _ | Y |

| WBZ451             | 1024                | 120              | 39   | LGA         | 4      | *                  | 2/1                 |      | 10           |     | 1/2     | 1   |     | '                     | 52                      | 4                        | 29        | 2                             | 8              | 1                  |     | ľ    |                                 | 1                       | 12                 | ľ             | 1                   |   |   |   |   |   |   |   |   |

| WBZ450             |                     |                  | 30   | LGA         | 2      |                    |                     |      |              |     |         |     |     |                       |                         |                          | 16        | 1                             | 6              |                    |     |      |                                 |                         | 4                  |               |                     |   |   |   |   |   |   |   |   |

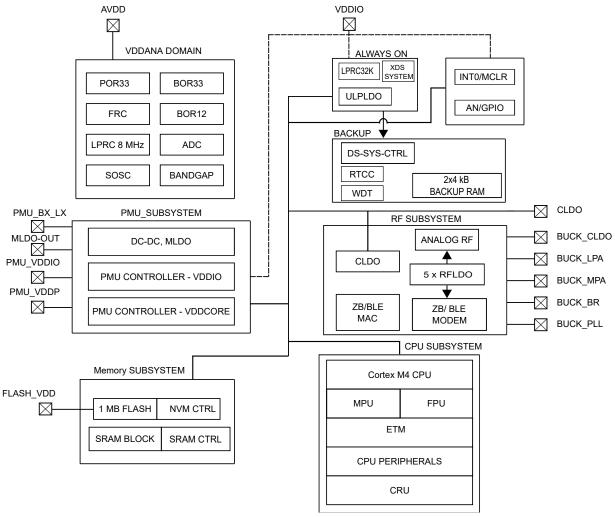

### 3. PIC32CX-BZ2 SoC Description

This chapter contains device-specific information for the PIC32CX-BZ2 SoC.

**Note:** Traditional AHB and APB documentation uses the terminology "Master" and "Slave". The equivalent Microchip terminology used in this document is "Manager" and "Subordinate", respectively.

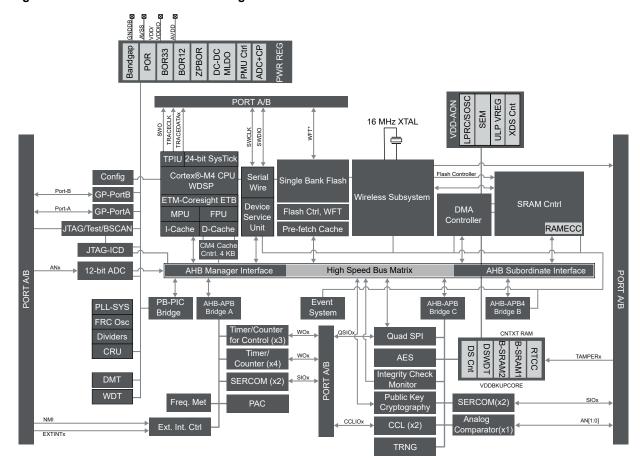

### 3.1 PIC32CX-BZ2 SoC Block Diagram

The following figure illustrates the block diagram of the core and peripheral modules in the PIC32CX-BZ2 SoC.

Figure 3-1. PIC32CX-BZ2 SoC Block Diagram

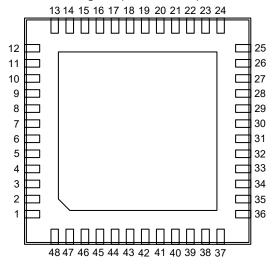

### 3.2 Pinout Diagram

This section provides details on pin diagrams for each variant of the PIC32CX-BZ2 SoC.

PIC32CX-BZ2 SoC Description

Figure 3-2. PIC32CX1012BZ25048 SoC Pin Diagram (Bottom View)

### PIC32CX1012BZ25048

### Note:

1. It is required that the exposed paddle on the bottom of the SoC be connected to ground in the PCB.

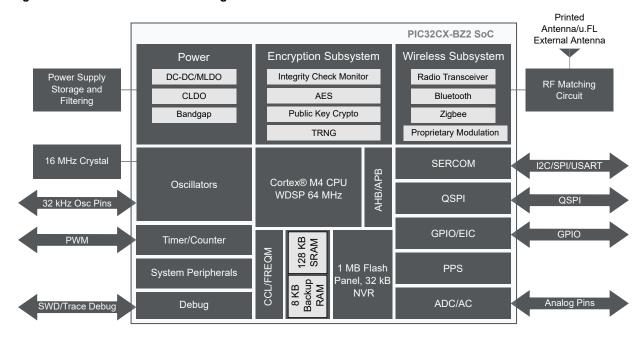

### 4. WBZ45 Module Description

The WBZ45 contains the PIC32CX-BZ2 SoC with following antenna options:

- · PCB antenna

- · u.FL connector for external antenna

The following figure represents the WBZ45 module block diagram.

Figure 4-1. WBZ45 Module Block Diagram

### 4.1 Pinout Diagram

The following figure illustrates the module pinout diagram.

Figure 4-2. WBZ451 Module Pin Diagram (Top View)

WBZ451

Note: It is required that the exposed paddle on the bottom of the module be connected to ground in the PCB.

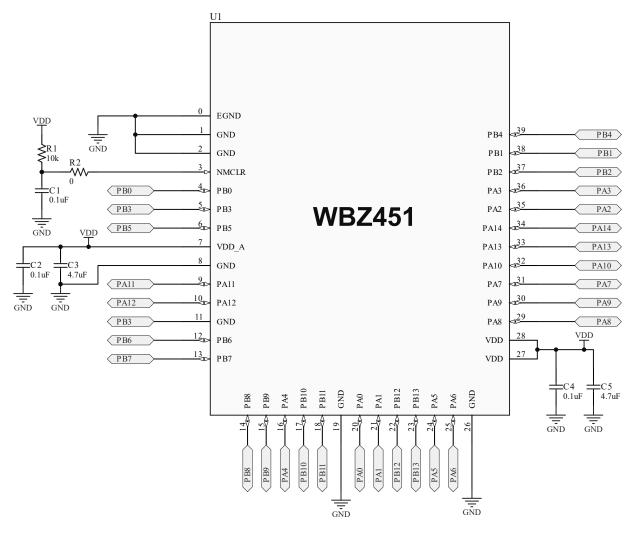

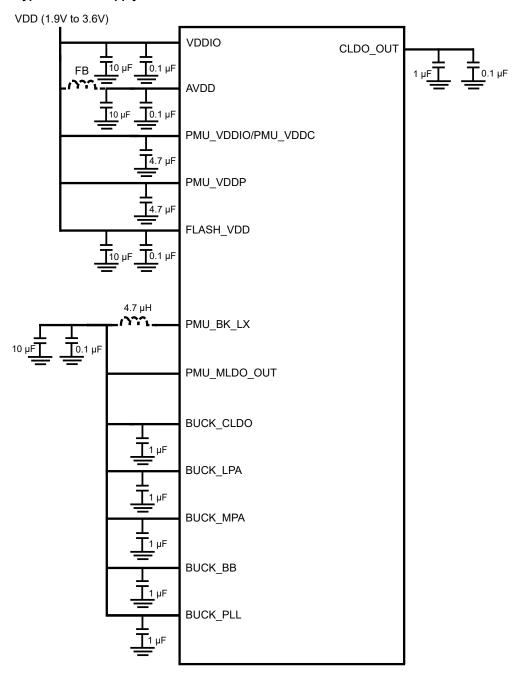

### 4.2 Basic Connection Requirement

The WBZ45 module requires attention to a minimal set of device pin connections before proceeding with development.

Figure 4-3. Module Basic Connection and Interface Diagram

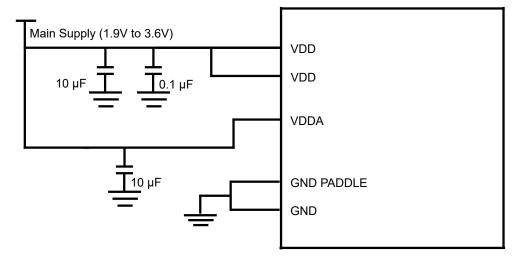

#### 4.2.1 Power Pins

It is recommended that a bulk and a decoupling capacitor be added at the input supply pin (VDD, VDD\_A and GND pins) of the WBZ45 module.

- It is recommended that 4.7 μF be on the VDD A pin and 4.7 μF and a 0.1 μF be on the VDD pin.

- The value of the capacitors are based on typical application requirements and are the minimum recommended values. Depending on the application requirement (in other words, a noisy power line or other known noise sources), the values of capacitors can be adjusted to provide a clean supply to the module.

- · All capacitors must be placed close to the Module Power supply pins.

#### 4.2.2 Master Clear (MCLR) Pin

The MCLR pin provides for two specific device functions:

- Device Reset

- Device programming and debugging

Pulling the  $\overline{\text{MCLR}}$  pin low generates a device Reset. Module Basic Connection and Interface Diagram illustrates a typical  $\overline{\text{MCLR}}$  circuit, see the *Module Basic Connection and Interface Diagram* in the *Basic Connection Requirement* from Related Links.

The module has sufficient filtering (0.1  $\mu$ F) and pull-up (10k) on the Reset line. On a typical application, no extra filtering is required on this pin.

**WBZ45 Module Description**

#### **Related Links**

4.2. Basic Connection Requirement

#### 4.2.3 SWD Lines

The CM4\_SWCLK, CM4\_SWDIO and CM4\_SWO pins are used for SWD Programming and debugging purposes. It is recommended that the CM4\_SWCLK and CM4\_SWDIO pin be used for the WBZ45 module for SWD as the default configuration (CM4\_SWO can be optional).

Keep the trace length between the SWD pins of the WBZ45 module and the SWD header as short as possible. If the SWD connector is expected to experience an ESD event, a series resistor is recommended with the value in the range of a few tens of  $\Omega$ s, not to exceed  $100\Omega$ .

Note: Provide an option for adding an external pull-up on SWDIO.

#### 4.2.4 Unused I/O Pins

It is recommended that unused I/O pins not be allowed to float as inputs. They can be configured as inputs and pulled up. Alternatively, depending on the application, they can be pulled down as well.

**Note:** Pin PA3 has to be pulled down for optimal power consumption.

#### 4.2.4.1 GPIO Pins/PPS Functions

Most of the WBZ45 module pins can be configured as GPIOs pins or for PPS functionality. To find the functionality supported by each of these GPIOs, see *I/O Ports and Peripheral Pin Select (PPS)* from Related Links. It is recommended that a series resistor be added on the host board for all critical, high frequency pins and clocks for EMI considerations. The value of the series resistor depends on the actual pin configuration. These resistors must be placed close to the module. Example of Host Board on Top Layer illustrates the placement of the series resistor; see the *Example of Host Board on Top Layer* figure in the *WBZ45 Module Routing Guidelines* from Related Links.

#### **Related Links**

6. I/O Ports and Peripheral Pin Select (PPS)

4.4. WBZ45 Module Routing Guidelines

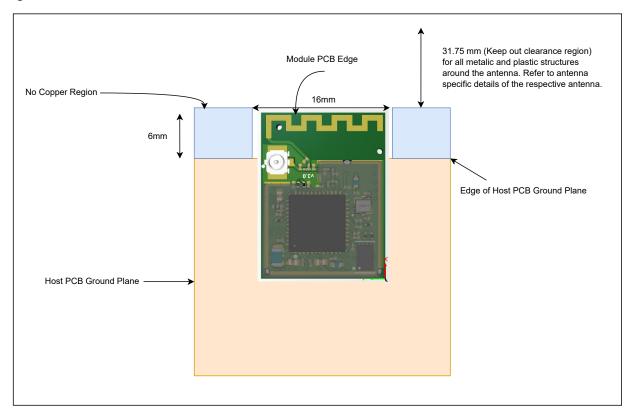

#### 4.3 WBZ45 Module Placement Guidelines

- For any Bluetooth Low Energy/Zigbee product, the antenna placement affects the performance of the whole system. The antenna requires free space to radiate RF signals and it must not be surrounded by the ground plane. Thus, for the best PCB antenna performance, it is recommended that the WBZ45 module be placed at the edge of the host board.

- It is recommended that the WBZ45 module ground outline edge be aligned with the edge of the host board ground plane as shown in the following figure.

- A low-impedance ground plane for the WBZ45 module ensures the best radio performance (best range and lowest noise). The ground plane can be extended beyond the minimum recommendation as required for the host board EMC and noise reduction.

- For the best performance, keep metal structures and components (such as mechanical spacers, bump-on and so on) at least 31.75 mm away from the PCB trace antenna as illustrated in the following figure.

- It is recommended that the antenna on the WBZ45 module not be placed in direct contact with or in close

proximity to plastic casing or objects. Keep a minimum clearance of 10 mm in all directions around the PCB

antenna as shown in the following figure. Keeping metallic and plastic objects close to the antenna can detune

the antenna and reduce the performance of the device.

- Exposed GND pads on the bottom of the WBZ45 module must be soldered to the host board (see the Example of Host Board on Top Layer figure in the WBZ45 Module Routing Guidelines from Related Links).

- A PCB cutout or a copper keepout is required under the RF test point (see WBZ451 Module Packaging Information from Related Links).

- Copper keepout areas are required on the top layer under voltage test points (see WBZ451 Module Packaging Information from Related Links).

- Alternatively, the entire region, except the exposed ground paddle, can be solder-masked.

The following figure illustrates the examples of WBZ45 module placement on a host board with a ground plane. Refer to the following figure for placement-specific guidance.

Figure 4-4. Module Placement Guidelines

### **Related Links**

- 4.4. WBZ45 Module Routing Guidelines

- 44.2. WBZ451 Module Packaging Information

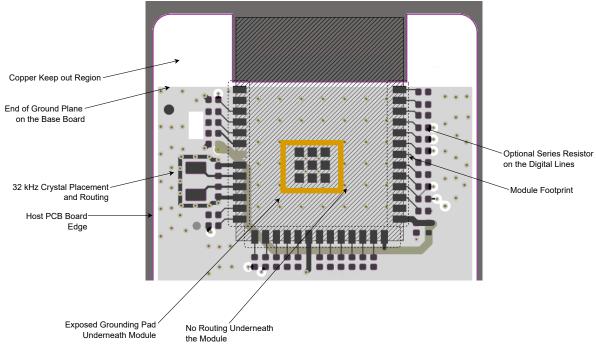

### 4.4 WBZ45 Module Routing Guidelines

- · Use the multi-layer host board for routing signals on the inner layer and the bottom layer.

- The top layer (underneath the module) of the host board must be ground with as many GND vias as possible, shown in the following figure.

- Avoid fan-out of the signals under the module or antenna area. Use a via to fan-out signals to theedge of the WBZ45 module.

- For a better GND connection to the WBZ45 module, solder the exposed GND pads of the WBZ45 module on the host board.

- For the module GND pad, use a GND via of a minimum 10 mil (hole diameter) for good ground to all the layers and thermal conduction path.

- Having a series resistor on the host board for all GPIOs is recommended. These resistors must be placed close

to the WBZ45 module. Refer to the following figure for the placement of the series resistor.

- The SOSC crystal (32.768 kHz) on the host board must be placed close to the WBZ45 module and follow the shortest trace routing length with no vias (see the following figure).

Figure 4-5. Example of Host Board on Top Layer

#### 4.5 WBZ45 Module RF Considerations

The overall performance of the system is significantly affected by the product design, environment and application. The product designer must ensure system-level shielding (if required) and verify the performance of the product features and applications.

Consider the following guidelines for optimal RF performance:

- The WBZ45 module must be positioned in a noise-free RF environment and must be kept far away from high-frequency clock signals and any other sources of RF energy.

- The antenna must not be shielded by any metal objects.

- · The power supply must be clean and noise-free.

- Make sure that the width of the traces routed to GND, VDD rails are sufficiently large for handling peak TX current consumption.

Note: The WBZ45 module includes RF shielding on top of the board as a standard feature.

#### 4.6 WBZ45 Module Antenna Considerations

#### 4.6.1 PCB Antenna

For the WBZ45 module, the PCB antenna is fabricated on the top copper layer and covered in a solder mask. The layers below the antenna do not have copper trace. It is recommended that the module be mounted on the edge of the host board and to have no PCB material below the antenna structure of the module and no copper traces or planes on the host board in that area.

The following table lists the technical specification of the PCB antenna when tested with the WBZ45 module mounted on an Evaluation Board.

**WBZ45 Module Description**

Table 4-1. PCB Antenna Specification for WBZ45

| Parameter           | Specification        |

|---------------------|----------------------|

| Operating frequency | 2400 to 2480 MHz     |

| Peak gain           | 2.36 dBi at 2420 MHz |

| Efficiency          | 50%                  |

#### 4.6.2 External Antenna Placement Recommendations

The following recommendations must be applied for the placement of the antenna and its cable:

- The antenna cable must not be routed over circuits generating electrical noise on the host board or alongside or underneath the module. It is preferred that the cable is routed straight out of the module.

- The antenna must not be placed in direct contact or in close proximity of the plastic casing/objects. (Except when the selected antenna specifically recommends it).

- Do not enclose the antenna within a metal shield.

- Keep any components that may radiate noise, signals or harmonics within the 2.4-2.5 GHz frequency band away from the antenna and, if possible, shield those components. Any noise radiated from the host board in this frequency band degrades the sensitivity of the module.

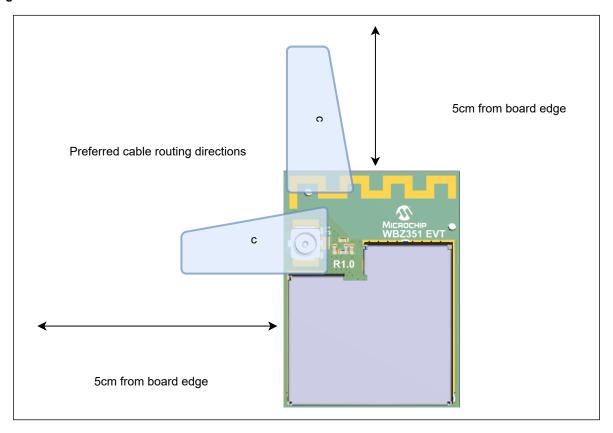

- The antenna must be placed at a distance greater than 5 cm away from the module. The following figure illustrates the antenna keepout area where the antenna must not be placed.

These recommendations are based on an open-air measurement and do not take into account any metal shielding of the customer end product. When a metal enclosure is used, the antenna can be located closer to the WBZ45 Module.

**Note:** These are generic guidelines and it is recommended that customers check and fine-tune the antenna positioning in the final host product based on RF performance.

The following figure illustrates an indication on how to route the antenna cable depending on the location of the antenna with respect to the WBZ45 PCB; there are two possible options for the optimum routing of the cable.

Figure 4-6. WBZ45 Antenna Placement Guidelines

Table 4-2. List of Certified Antenna

| Serial Number | Part Number     | Vendor            | Antenna Type | Gain     | Comment                |

|---------------|-----------------|-------------------|--------------|----------|------------------------|

| 1             | W3525B039       | Pulse             | РСВ          | 2 dBi    | Cable length 100 mm    |

| 2             | 001-0016        | LSR               | PIFA         | 2.5 dBi  | Flex PIFA antenna      |

| 3             | 001-0001        | LSR               | Dipole       | 2 dBi    | RPSMA connector*       |

| 4             | 1461530100      | Molex             | PCB          | 3 dBi    | 100 mm (Dual Band)     |

| 5             | ANT-2.4-LPW-125 | Linx Technologies | Dipole       | 2.8 dBi  | 125 mm                 |

| 6             | RFA-02-P05-D034 | Alead             | PCB          | 2 dBi    | 150 mm                 |

| 7             | RFA-02-P33-D034 | Alead             | РСВ          | 2 dBi    | 150 mm                 |

| 8             | ABAR1504-S2450  | ABRACON           | PCB          | 2.28 dBi | 250 mm                 |

| 9             | WBZ451 LGA      | _                 | _            | 2.36 dBi | Only for WBZ451 module |

| 10            | WBZ450 LGA      | _                 | _            | 4.14 dBi | Only for WBZ450 module |

### 4.7 WBZ45 Module Reflow Profile Information

The WBZ45 module was assembled using the IPC/JEDEC J-STD-020 Standard lead free reflow profile. The WBZ45 module can be soldered to the host board using standard leaded or lead-free solder reflow profiles. To avoid damaging the module, adhere to the following recommendations:

• For Solder Reflow Recommendations, refer to the Solder Reflow Recommendation Application Note (AN233).

**WBZ45 Module Description**

- Do not exceed a peak temperature (TP) of 250°C.

- · Refer to the solder paste data sheet for specific reflow profile recommendations from the vendor.

- · Use no-clean flux solder paste.

- · Do not wash as moisture can be trapped under the shield.

- Use only one flow. If the PCB requires multiple flows, apply the module on the final flow.

#### 4.7.1 Cleaning

The exposed GND pad helps to self-align the module, avoiding pad misalignment. The recommendation is to use the no clean solder pastes. Ensure full drying of no-clean paste fluxes as a result of the reflow process. As per the recommendation by the solder paste vendor, this requires longer reflow profiles and/or peak temperatures toward the high end of the process window. The uncured flux residues can lead to corrosion and/or shorting in accelerated testing and possibly the field.

### 4.8 WBZ45 Module Assembly Considerations

The WBZ45 module is assembled with an EMI shield to ensure compliance with EMI emission and immunity rules. The EMI shield is made of a tin-plated steel (SPTE) and is not hermetically sealed. Use the solutions such as IPA and similar solvents to clean this module. Cleaning solutions containing acid must never be used on the module.

#### 4.8.1 Conformal Coating

The modules are not intended for use with a conformal coating, and the customer assumes all risks (such as the module reliability, performance degradation and so on) if a conformal coating is applied to the modules.

### 5. Pinout and Signal Descriptions List

The following table provides details on signal names classified by the peripherals along with the device pinout for each variant of the PIC32CX-BZ2 SoC and WBZ45 module.

Table 5-1. Pinout and Signal Descriptions List

| PIC32CX | -BZ2 SoC | WBZ45                     | Module                    |           | Peripherals |     |        |                        |            |             |              |     |           |                     |

|---------|----------|---------------------------|---------------------------|-----------|-------------|-----|--------|------------------------|------------|-------------|--------------|-----|-----------|---------------------|

| 24032   | 25048    | 450                       | 451                       | Pad Name  | AC          | ADC | EIC(4) | <sub>GPIO</sub> (1, 2) | QSPI       | RTCC        | SERCOM       | osc | RF        | DEBUG               |

|         |          | 1, 5, 8,<br>18, 21,<br>27 | 1, 2, 8,<br>11, 19,<br>26 | GND       |             |     |        |                        |            |             |              |     |           |                     |

| 32      | 1        |                           |                           | PMU_BK    |             |     |        |                        |            |             |              |     |           |                     |

| 1       | 2        |                           |                           | VPMU_VDD  |             |     |        |                        |            |             |              |     |           |                     |

| 2       | 3        |                           |                           | PMU_MLDO  |             |     |        |                        |            |             |              |     |           |                     |

|         | 4        |                           | 20                        | PA0       |             |     |        | RA0                    | QSPI_DATA2 | RTC_IN3     |              |     |           |                     |

|         | 5        |                           | 21                        | PA1       | AC_CMP1     |     |        | RA1                    | QSPI_DATA3 | RTC_IN2     |              |     |           |                     |

|         | 6        |                           | 35                        | PA2       | AC_CMP0     |     |        | RA2                    |            | RTC_IN1     |              |     |           |                     |

| 3       | 7        | 19                        | 24                        | PA5       |             |     |        | RA5                    |            |             | SERCOM0_PAD0 |     |           |                     |

| 4       | 8        | 16, 17                    | 27, 28                    | VDD       |             |     |        |                        |            |             |              |     |           |                     |

| 5       | 9        | 20                        | 25                        | PA6       | AC_CMP1_ALT |     |        | RA6                    |            |             | SERCOM0_PAD1 |     |           | PGC2ENTRY           |

| 6       | 10       | 25                        | 31                        | PA7       |             |     |        | RA7                    |            |             | SERCOM1_PAD0 |     |           | TRACECLK            |

| 7       | 11       | 24                        | 29                        | PA8       |             |     |        | RA8                    |            |             | SERCOM1_PAD1 |     | FECTRL0   | PGD2ENTRY           |

| 8       | 12       | 22                        | 30                        | PA9       |             |     |        | RA9                    |            | RTC_IN0_ALT | SERCOM1_PAD2 |     | FECTRL1   |                     |

| 9       | 13       | 23                        | 32                        | PA10      |             |     |        | RA10                   |            | RTC_OUT_ALT | SERCOM1_PAD3 |     | FECTRL2   |                     |

|         | 14       |                           | 22                        | PB12      |             |     |        | RB12                   | QSPI_DATA0 |             |              |     |           |                     |

|         | 15       |                           | 23                        | PB13      |             |     |        | RB13                   | QSPI_DATA1 | RTC_EVENT   |              |     |           |                     |

|         | 16       |                           | 33                        | PA13      |             |     |        | RA13                   |            |             | SERCOM2_PAD0 |     | COEXCTRL0 |                     |

|         | 17       |                           | 34                        | PA14      |             |     |        | RA14                   |            |             | SERCOM2_PAD1 |     | COEXCTRL1 |                     |

| 10      | 18       |                           |                           | CLDO_O    |             |     |        |                        |            |             |              |     |           |                     |

| 11      | 19       |                           |                           | BUCK_CLDO |             |     |        |                        |            |             |              |     |           |                     |

| 12      | 20       |                           |                           | EXTR(8)   |             |     |        |                        |            |             |              |     |           |                     |

| 13      | 21       |                           |                           | BUCK_BB   |             |     |        |                        |            |             |              |     |           |                     |

| 14      | 22       |                           |                           | XO_N      |             |     |        |                        |            |             |              | XO- |           |                     |

| 15      | 23       |                           |                           | XO_P      |             |     |        |                        |            |             |              | XO+ |           |                     |

| 16      | 24       |                           |                           | BUCK_PLL  |             |     |        |                        |            |             |              |     |           |                     |

| 17      | 25       |                           |                           | BUCK_LPA  |             |     |        |                        |            |             |              |     |           |                     |

| 18      | 26       |                           |                           | LPA_OUT   |             |     |        |                        |            |             |              |     | LPA       |                     |

|         | 27       |                           |                           | MPA_OUT   |             |     |        |                        |            |             |              |     | MPA       |                     |

|         | 28       |                           |                           | BUCK_MPA  |             |     |        |                        |            |             |              |     |           |                     |

|         | 29       | 2                         | 3                         | NMCLR     |             |     |        |                        |            |             |              |     |           |                     |

| 20      | 30       | 3                         | 4                         | PB0       | AC_AIN2     | AN4 |        | RB0                    |            |             |              |     | COEXCTRL2 |                     |

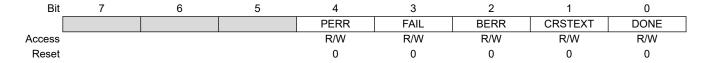

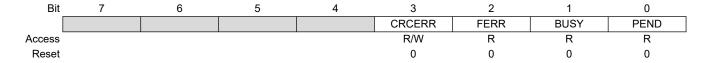

| 21      | 31       | 10                        | 38                        | PB1       | AC_AIN3     | AN5 |        | RB1                    |            |             |              |     |           |                     |