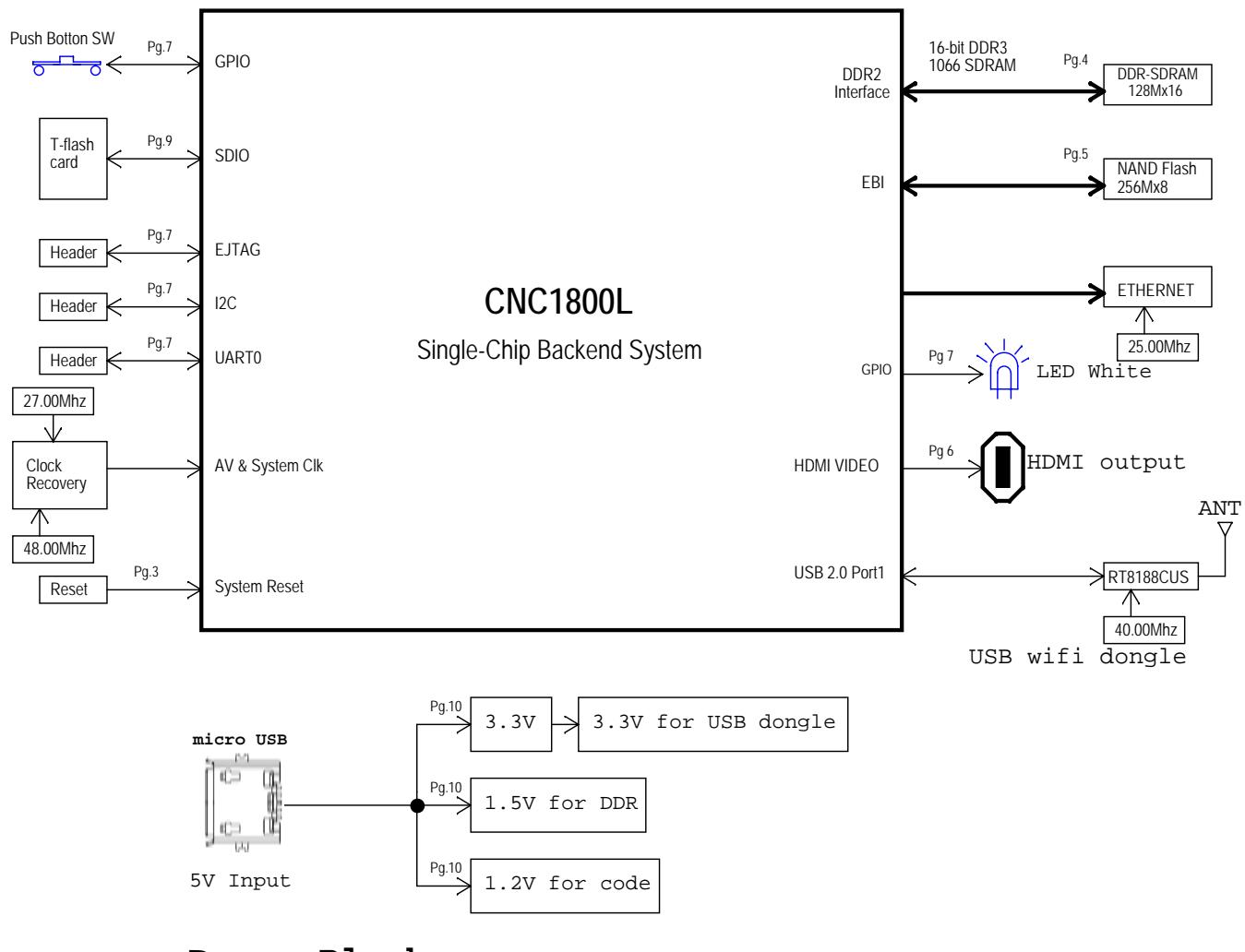

# 1OTT Block Diagram

| Revision History: |                     |            |          |

|-------------------|---------------------|------------|----------|

| Rev               | Description         | Date       | Approved |

| 1                 | Preliminary Release | 2012/09/19 |          |

|                   |                     |            |          |

|                   |                     |            |          |

|                   |                     |            |          |

## Layout Notes:

1. Discrete (especially resistors) should be placed close to Large components which are on the same schematic page

NOTES, UNLESS OTHERWISE SPECIFIED:

1. RESISTANCE VALUES IN OHMS.

2. CAPACITANCE VALUES IN MICROFARADS.

3. REFERENCE DESIGNATORS USED.

4. ALL 0.1  $\mu$ F CAPACITORS ARE DECOUPLING CAPS UNLESS OTHERWISE NOTED. THEY ARE SHOWN ON THE PAGE WITH THE INTEGRATED CIRCUITS THEY SHOULD BE PLACED NEAR.

### 5. BOARD PROPERTIES:

- A. FR-4 RoHS COMPLIANT MATERIAL PER IPC-4101/129 OR BETTER

- B. ALL SIGNAL LAYERS - 0.5 OZ CU

- C. PLANE LAYERS - 0.5 OZ CU

- D. IMPEDANCE CONTROL:

50 OHMS +/- 10% SINGLE ENDED TRACES

60 OHMS +/- 10% SINGLE ENDED TRACES

90 OHMS +/- 10% SINGLE ENDED TRACES

100 OHMS +/- 10% DIFFERENTIAL TRACES

- E. LAYER STACKUP:

**Syabas Technology Inc.**

Room 718,7th Floor, Building 202,Tairan Hi-Tech Garden,Futian District,ShenZhen,China.

Title

Size B Document Number

Rev 1.0

Date: Friday, June 21, 2013

Sheet 2 of 9