Guinea Tech.

# Bluetooth® Low Energy Module

#### Introduce

The module base on Renesas RA4W1 MCU which in included a BLE v5.0 RF modem and other rich peripheral. It support BLE stack and Software and relative IO for user development.

#### **Features**

#### Arm Cortex-M4 Core with Floating Point Unit (FPU)

Armv7E-M architecture with DSP instruction set

Maximum operating frequency: 48 MHz

Support for 4-GB address space

Arm Memory Protection Unit (Arm MPU) with 8 regions

Debug and Trace: ITM, DWT, FPB, TPIU, and ETB

#### Memory

512-KB code flash memory

8-KB data flash memory (100,000 erase/write cycles)

96-KB SRAM

Flash Cache (FCACHE)

**Memory Protection Units**

Memory Mirror Function (MMF)

128-bit unique ID

#### ■ Connectivity

Bluetooth Low Energy

- > Bluetooth 5.0 core specification compliant BLE transceiver and link layer

- Supporting LE 1M and Coded PHY, and LE Advertising extension

- Dedicated AES-CCM (128-bit blocks) encryption circuit

USB 2.0 Full-Speed (USBFS) module

- On-chip transceiver

- > Compliant with USB Battery Charging Specification 1.2

Serial Communications Interface (SCI) × 4

- ➤ UART

- Simple IIC

- > Simple SPI

Serial Peripheral Interface (SPI) × 2

I2C bus interface (IIC) × 2

Controller Area Network (CAN) module

#### ■ Analog

14-bit A/D Converter (ADC14)

12-bit D/A Converter (DAC12)

8-bit D/A Converter (DAC8) ×2 (for ACMPLP)

Low Power Analog Comparator (ACMPLP) × 2

Operational Amplifier (OPAMP) × 1

Temperature Sensor (TSN)

#### Timers

General PWM Timer 32-bit (GPT32) × 4

Guinea Tech. GDS-B51

General PWM Timer 16-bit (GPT16) × 3

Asynchronous General-Purpose Timer (AGT)  $\times$  2

Watchdog Timer (WDT)

#### Safety

Error Correction Code (ECC) in SRAM

SRAM parity error check

Flash area protection

ADC self-diagnosis function

Clock Frequency Accuracy Measurement Circuit (CAC)

Cyclic Redundancy Check (CRC) calculator

Data Operation Circuit (DOC)

Port Output Enable for GPT (POEG)

Independent Watchdog Timer (IWDT)

GPIO readback level detection

Register write protection

Main oscillator stop detection

Illegal memory access

#### System and Power Management

Low power modes

Realtime Clock (RTC) with calendar and Battery Backup support

Event Link Controller (ELC)

DMA Controller (DMAC) × 4

Data Transfer Controller (DTC)

Key Interrupt Function (KINT)

Power-on reset

Low Voltage Detection (LVD) with voltage settings

#### Security and Encryption

AES128/256

**GHASH**

True Random Number Generator (TRNG)

#### ■ Human Machine Interface (HMI)

Segment LCD Controller (SLCDC)

- ➤ Up to 9 segments × 4 commons

- Capacitive Touch Sensing Unit (CTSU)

#### Multiple Clock Sources

Main clock oscillator (MOSC)

- ightharpoonup (1 to 20 MHz when VCC = 2.4 to 3.6 V)

- ightharpoonup (1 to 8 MHz when VCC = 1.8 to 2.4 V)

Sub-clock oscillator (SOSC) (32.768 kHz)

High-speed on-chip oscillator (HOCO)

- $\triangleright$  (24, 32, 48, 64 MHz when VCC = 2.4 to 3.6 V)

- (24, 32, 48 MHz when VCC = 1.8 to 3.6 V)

Middle-speed on-chip oscillator (MOCO) (8 MHz)

Low-speed on-chip oscillator (LOCO) (32.768 kHz)

IWDT-dedicated on-chip oscillator (15 kHz)

Clock trim function for HOCO/MOCO/LOCO

Clock out support

#### General Purpose I/O Ports

Up to 35 input/output pins

- Up to 3 CMOS input

- Up to 32 CMOS input/output

- Up to 4 input/output 5 V tolerant

• Up to 1 high current (20 mA)

#### Operating Voltage

VCC: 1.8 to 3.6 V

#### ■ Module

Certified to FCC, ISED, CE, KCC, NCC and SRRC

On-Board Bluetooth Low Energy (BLE) Stack

ASCII Command Interface API Over UART

Scripting Engine for Hostless Operation

Compact Form Factor – 20 \* 16 mm

$Ta = -40^{\circ}C$  to  $+85^{\circ}C$

## **Contents**

| 1.   | Module overview                    | 5  |

|------|------------------------------------|----|

| 1.1  | overview                           | 5  |

| 1.2  | Bluetooth Low Energy specification | 6  |

| 2.   | Specification                      | 7  |

| 2.1  | Pin description                    | 7  |

| 2.2  | Dimension                          | 16 |

| 3.   | Characteristic                     | 18 |

| 3.1. | BLE Characteristics                | 18 |

|      | MCU Characteristics                |    |

| Rev  | vision Record                      | 28 |

#### 1. Module Overview

#### 1.1 Overview

The module integrated ARM Cortex M4 and Bluetooth5.0 baseband controller , on -board Bluetooth stack, Digital and Analog I/Os in to one solution .

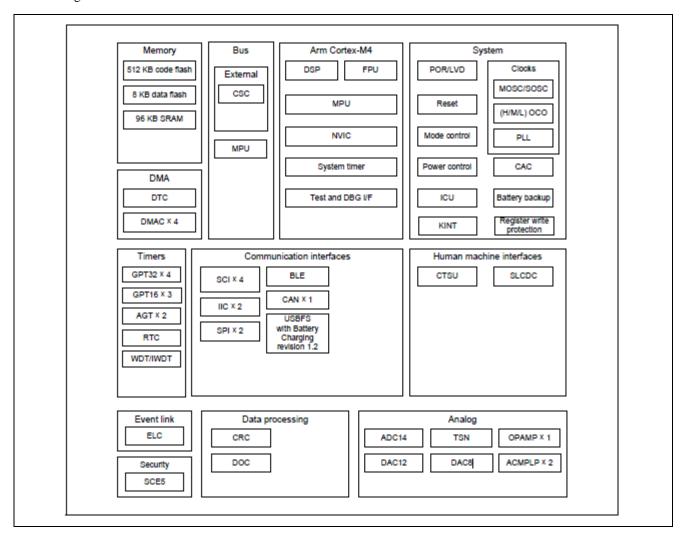

Block diagram of MCU

## 1.2 Bluetooth Low Energy (BLE)

This MCU has a Bluetooth Low Energy (BLE), which consists of an RF transceiver compliant with Bluetooth 5.0 Low

Energy (single mode), a link layer, and an RF transceiver power-supply.

The BLE is controlled by a Bluetooth middleware available from Renesas Electronics Corporation.

### Specifications of the BLE

| ltem            | Description                                                                                   |                                         |                                                                                                                       |  |  |

|-----------------|-----------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| Features        | <ul> <li>An on-chip matchin</li> <li>On-chip BLE-dedica</li> <li>Transmission powe</li> </ul> |                                         |                                                                                                                       |  |  |

| Bluetooth 5.0   | Classification                                                                                | Function                                | Remark                                                                                                                |  |  |

| functions       | Device Address                                                                                | Public or random address                | The address can be set as a desired address.                                                                          |  |  |

|                 | Advertising                                                                                   | Extended or periodic                    |                                                                                                                       |  |  |

|                 |                                                                                               | Multiple advertising                    | Maximum number of sets: 4                                                                                             |  |  |

|                 |                                                                                               | Advertising or Scan Response<br>Data    | Maximum data length=1650 bytes                                                                                        |  |  |

|                 | Scanning                                                                                      | Passive, active, or periodic            | Number of units for concurrent synchronization with periodic advertising=2                                            |  |  |

|                 |                                                                                               | Whitelist or periodic advertiser list   | Number of units registered in the whitelist: 4<br>Number of units registered in the periodic<br>advertiser list: 4    |  |  |

|                 | Master or slave                                                                               | Data transmission or reception          | Maximum payload length=251 bytes<br>MoreData function is supported.<br>Master/slave multi-role function is supported. |  |  |

|                 | Other                                                                                         | Bit rates                               | 125 kbps, 500 kbps, 1 Mbps, 2 Mbps<br>Bit-rate combinations for transmission and<br>reception can be set as desired.  |  |  |

|                 |                                                                                               | Frequency hopping                       | Channel Selection Algorithm #2                                                                                        |  |  |

|                 |                                                                                               | Encryption circuit for Bluetooth        | On-chip Bluetooth-dedicated AES-CCM (128 bits) circuit                                                                |  |  |

| Other functions | RF transceiver power                                                                          | r-supply (DC-to-DC converter, and lines | ar regulator)                                                                                                         |  |  |

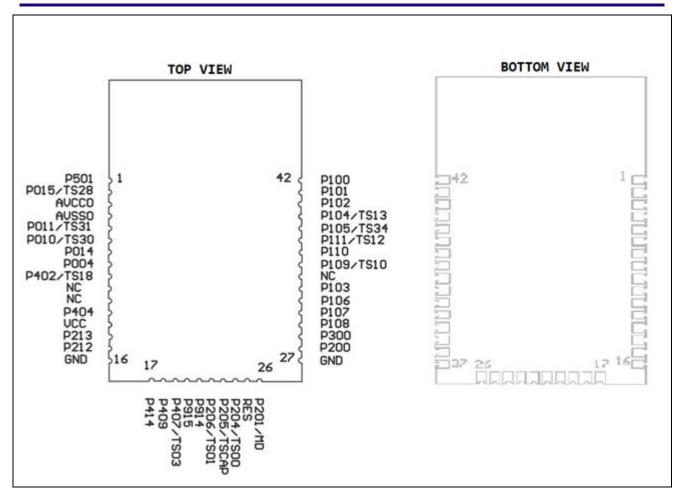

Application board top view

## 2. Specification

## **Pins Description**

| Pin | Description                                                             | Remark                                                                                  |

|-----|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 1   | P501/USB_OVRCURA/ AN017                                                 | General purpose Input/Output pins                                                       |

| 2   | P015/TS28/ AN010                                                        | General purpose Input/Output pins Capacitive Touch detection pin                        |

| 3   | AVCC0                                                                   | Analog block power supply pin                                                           |

| 4   | AVSS0                                                                   | Analog block power supply ground pin                                                    |

| 5   | P011/TS31/ AN006/ AMP2+                                                 | General purpose Input/Output pins<br>Capacitive Touch detection pin                     |

| 6   | P010/TS30/ AN005/ AMP2-                                                 | General purpose Input/Output pins<br>Capacitive Touch detection pin                     |

| 7   | P014/ AN009/ DA0                                                        | General purpose Input/Output pins                                                       |

| 8   | P004/ AN004/ AMP2O                                                      | General purpose Input/Output pins                                                       |

| 9   | P402/TS18/RXD1/<br>MISO1/SCL1/ CRX0                                     | General purpose Input/Output pins<br>Capacitive Touch detection pin                     |

| 10  | X                                                                       | N/C                                                                                     |

| 11  | X                                                                       | N/C                                                                                     |

| 12  | P404                                                                    | General purpose Input/Output pins                                                       |

| 13  | MCU-VCC                                                                 | Power supply pin                                                                        |

| 14  | P213/TXD1/MOSI1/SDA1                                                    | General purpose Input/Output pins                                                       |

| 15  | P212/RXD1/MISO1 /SCL1                                                   | General purpose Input/Output pins                                                       |

| 16  | GND                                                                     | Ground pin                                                                              |

| 17  | P414/SSLA1                                                              | General purpose Input/Output pins                                                       |

| 18  | P409/ USB_EXICEN                                                        | General purpose Input/Output pins                                                       |

| 19  | P407/TS03/CTS4_RTS4<br>/SS4/SDA0/USB_VBUS/ADTRG0                        | General purpose Input/Output pins<br>Capacitive Touch detection pin                     |

| 20  | P915/USB_DM                                                             | General purpose Input/Output pins                                                       |

| 21  | P914/USB_DP                                                             | General purpose Input/Output pins                                                       |

| 22  | P206/TS01/RXD4/MISO4/SCL4<br>/SDA1/SSLB1/USB_VBUSEN                     | General purpose Input/Output pins<br>Capacitive Touch detection pin                     |

| 23  | P205/TSCAP/TXD4/MOSI4<br>/SDA4/CTS9_RTS9/SS9<br>/SCL1/SSLB0/USB_OVRCURA | General purpose Input/Output pins<br>Secondary power supply pin for the<br>touch driver |

| 24  | P204/TS00/SCK4/SCK9/SCL0<br>/RSPCKBUSB_OVRCURB                          | General purpose Input/Output pins<br>Capacitive Touch detection pin                     |

| 25  | RES                                                                     | Reset pin                                                                               |

| 26  | P201/MD                                                                 | General purpose Input/Output pins<br>Chip Operation mode                                |

| 27 | GND                                                | Ground pin                                                                   |

|----|----------------------------------------------------|------------------------------------------------------------------------------|

| 28 | P200                                               | General purpose input pin                                                    |

| 29 | P300/SWCLK/SSLB1                                   | General purpose Input/Output pins<br>Serial wire clock pin                   |

| 30 | P108/CTS9_RTS9<br>/SS9/SSLB0                       | General purpose Input/Output pins<br>Serial wire debug data input/output pin |

| 31 | P107                                               | General purpose Input/Output pins                                            |

| 32 | P106/SSLA3                                         | General purpose Input/Output pins                                            |

| 33 | P103/CTS0_RTS0/SS0/ CTX0/<br>AN019                 | General purpose Input/Output pins                                            |

| 34 | X                                                  | N/C                                                                          |

| 35 | P109/TS10/SCK1/TXD9/MOSI9<br>/SDA9/MOSIB/CTX0      | General purpose Input/Output pins<br>Capacitive Touch detection pin          |

| 36 | P110/RXD9/MISO9 /SCL9<br>/MISOB/ CRX0              | General purpose Input/Output pins<br>Capacitive Touch detection pin          |

| 37 | P111/TS12/SCK9/RSPCKB                              | General purpose Input/Output pins<br>Capacitive Touch detection pin          |

| 38 | P105/TS34/SSLA2                                    | General purpose Input/Output pins<br>Capacitive Touch detection pin          |

| 39 | P104/TS13/SSLA1                                    | General purpose Input/Output pins<br>Capacitive Touch detection pin          |

| 40 | P102/SCK0/RSPCKA/ CRX0/<br>AN020/ADTRG0            | General purpose Input/Output pins                                            |

| 41 | P101/TXD0/MOSI0/SDA0<br>/CTS1_RTS1/SS1/SDA1 /MOSIA | General purpose Input/Output pins                                            |

| 42 | P100/RXD0/MISO0/SCL0<br>/SCK1/SCL1/MISOA           | General purpose Input/Output pins                                            |

#### Note:

MCU support SCI 4 channels, SPI 2channels and IIC 2 channels, CAN 1 channel, USB FS 1channel, communication interface. 14bit ADC 8channels, 12bit DAC 1 channel.

#### Serial Communication Interface:

The Serial Communications Interface (SCI) is configurable to five asynchronous and synchronous serial interfaces:

Asynchronous interfaces (UART and Asynchronous Communications Interface Adapter (ACIA))

8-bit clock synchronous interface

Simple IIC (master-only)

Simple SPI

Smart card interface.

| Channel | Pin name            | Input/Output | Function                                                                                                       |

|---------|---------------------|--------------|----------------------------------------------------------------------------------------------------------------|

| SCI0    | SCK0                | Input/Output | SCI0 clock input/output                                                                                        |

|         | RXD0/SCL0/<br>MISO0 | Input/Output | SCI0 receive data input<br>SCI0 I <sup>2</sup> C clock input/output<br>SCI0 slave transmit data input/output   |

|         | TXD0/SDA0/<br>MOSI0 | Input/Output | SCI0 transmit data output<br>SCI0 I <sup>2</sup> C data input/output<br>SCI0 master transmit data input/output |

|         | SS0/CTS0_RTS0       | Input/Output | SCI0 chip select input, active-low<br>SCI0 transfer start control input/output, active-low                     |

| Channel | Pin name            | Input/Output | Function                                                                                                       |

| SCI1    | SCK1                | Input/Output | SCI1 clock input/output                                                                                        |

|         | RXD1/SCL1/<br>MISO1 | Input/Output | SCI1 receive data input<br>SCI1 I <sup>2</sup> C clock input/output<br>SCI1 slave transmit data input/output   |

|         | TXD1/SDA1/<br>MOSI1 | Input/Output | SCI1 transmit data output<br>SCI1 I <sup>2</sup> C data input/output<br>SCI1 master transmit data input/output |

|         | SS1/CTS1_RTS1       | Input/Output | SCI1 chip select input, active-low<br>SCI1 transfer start control input/output, active-low                     |

| SCI4    | SCK4                | Input/Output | SCI4 clock input/output                                                                                        |

|         | RXD4/SCL4/<br>MISO4 | Input/Output | SCI4 receive data input<br>SCI4 I <sup>2</sup> C clock input/output<br>SCI4 slave transmit data input/output   |

|         | TXD4/SDA4/<br>MOSI4 | Input/Output | SCI4 transmit data output<br>SCI4 I <sup>2</sup> C data input/output<br>SCI4 master transmit data input/output |

|         | SS4/CTS4_RTS4       | Input/Output | SCI4 chip select input, active-low<br>SCI4 transfer start control input/output, active-low                     |

| SCI9    | SCK9                | Input/Output | SCI9 clock input/output                                                                                        |

|         | RXD9/SCL9/<br>MISO9 | Input/Output | SCI9 receive data input<br>SCI9 I <sup>2</sup> C clock input/output<br>SCI9 slave transmit data input/output   |

|         | TXD9/SDA9/<br>MOSI9 | Input/Output | SCI9 transmit data output<br>SCI9 I <sup>2</sup> C data input/output<br>SCI9 master transmit data input/output |

|         | SS9/CTS9_RTS9       | Input/Output | SCI9 chip select input, active-low<br>SCI9 transfer start control input/output, active-low                     |

#### • Serial Peripheral Interface (SPI)

The MCU provides two independent channels of the Serial Peripheral Interface (SPI). The SPI channels are capable of high-speed, full-duplex synchronous serial communications with multiple processors and peripheral devices.

| Channel | Pin name | I/O    | Function                 |  |  |

|---------|----------|--------|--------------------------|--|--|

| SPI0    | RSPCKA   | I/O    | Clock I/O                |  |  |

|         | MOSIA    | I/O    | Master transmit data I/O |  |  |

|         | MISOA    | I/O    | Slave transmit data I/O  |  |  |

|         | SSLA0    | I/O    | Slave selection I/O      |  |  |

|         | SSLA1    | Output | Slave selection output   |  |  |

|         | SSLA2    | Output | Slave selection output   |  |  |

|         | SSLA3    | Output | Slave selection output   |  |  |

| SPI1    | RSPCKB   | I/O    | Clock I/O                |  |  |

|         | MOSIB    | I/O    | Master transmit data I/O |  |  |

|         | MISOB    | I/O    | Slave transmit data I/O  |  |  |

|         | SSLB0    | I/O    | Slave selection I/O      |  |  |

|         | SSLB1    | Output | Slave selection output   |  |  |

|         | SSLB3    | Output | Slave selection output   |  |  |

#### ■ I2C Bus Interface (IIC)

The MCU has a 2-channel I2C Bus Interface (IIC). The IIC module conforms with and provides a subset of the NXP I2C (Inter-Integrated Circuit) bus interface functions.

| Channel | Pin name | I/O | Function                  |  |

|---------|----------|-----|---------------------------|--|

| IIC0    | SCL0     | I/O | IIC0 serial clock I/O pin |  |

|         | SDA0     | I/O | IIC0 serial data I/O pin  |  |

| IIC1    | SCL1     | I/O | IIC1 serial clock I/O pin |  |

|         | SDA1     | I/O | IIC1 serial data I/O pin  |  |

#### Controller Area Network (CAN) Module

The CAN module uses a message-based protocol to receive and transmit data between multiple slaves and masters in electromagnetically noisy applications. The module complies with the ISO 11898-1 (CAN 2.0A/CAN 2.0B) standard and supports up to 32 mailboxes, which can be configured for transmission or reception in normal mailbox and FIFO modes. Both standard (11-bit) and extended (29-bit) messaging formats are supported. The CAN module requires an additional external CAN transceiver.

| Pin name | I/O    | Function          |  |

|----------|--------|-------------------|--|

| CRX0     | Input  | Data receive pin  |  |

| CTX0     | Output | Data transmit pin |  |

|          |        |                   |  |

#### USB 2.0 Full-Speed Module (USBFS)

The MCU provides a USB 2.0 Full-Speed module (USBFS) that operates as a host or device controller compliant with the Universal Serial Bus (USB) specification revision 2.0. The host controller supports USB 2.0 full-speed and low speed transfers, and the device controller supports USB 2.0 full-speed transfers. The USBFS has an internal USB transceiver and supports all of the transfer types defined in the USB 2.0 specification.

| Port   | Pin name                   | I/O    | Function                                                                                                                                                                                     |

|--------|----------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USBFS  | USB_DP                     | I/O    | D+ I/O pin for the on-chip USB transceiver.  Must be connected to the D+ pin of the USB bus.                                                                                                 |

|        | USB_DM                     | I/O    | D– I/O pin for the on-chip USB transceiver.  Must be connected to the D- pin of the USB bus.                                                                                                 |

|        | USB_VBUS                   | Input  | USB cable connection monitor pin.  Must be connected to VBUS signal on the USB bus. The VBUS pin status (connected or disconnected) can be detected when the USBFS is a device controller.*1 |

|        | USB_VBUSEN                 | Output | VBUS (5 √) enable signal for the external power supply IC                                                                                                                                    |

|        | USB_OVRCURA<br>USB_OVRCURB | Input  | Overcurrent pins for USBFS.  Must be connected to external overcurrent detection signals.                                                                                                    |

| Common | VCC_USB                    | Input  | Power supply for USB transceiver.                                                                                                                                                            |

|        | VCC_USB_LDO                | Input  | Power supply pin for USB transceiver. Apply the same voltage as VCC_USB                                                                                                                      |

|        | VSS USB                    | Input  | USB ground pin                                                                                                                                                                               |

#### ■ 14-Bit A/D Converter (ADC14)

The MCU provides a 14-bit successive approximation A/D converter (ADC14) unit. Up to 8 analog input channels are selectable. Temperature sensor output and internal reference voltage can be selected for conversion. The A/D conversion accuracy is 14-bit conversion, making it possible to optimize the trade-off between speed and resolution in generating a digital value.

| Unit   | Pin name                                                       | I/O   | Function                                               |

|--------|----------------------------------------------------------------|-------|--------------------------------------------------------|

| Unit 0 | AVCC0                                                          | Input | Analog block power supply pin                          |

|        | AVSS0                                                          | Input | Analog block power supply ground pin                   |

|        | ∨REFH0                                                         | Input | Reference power supply pin                             |

|        | VREFL0                                                         | Input | Reference power supply ground pin                      |

|        | AN004 to AN006,<br>AN009, AN010,<br>AN017, AN019,<br>and AN020 | Input | Analog input pins 4 to 6, 9, 10, 17, 19, and 20        |

|        | ADTRG0                                                         | Input | External trigger input pin for starting A/D conversion |

## ■ 12-Bit D/A Converter (DAC12)

The MCU provides a 12-bit D/A Converter (DAC12).

| Pin name | I/O    | Function                    |  |

|----------|--------|-----------------------------|--|

| DA0      | Output | Channel 0 analog output pin |  |

|          | Output | Channel o analog output pin |  |

|          |        |                             |  |

|          |        |                             |  |

## Inside MCU pin list of Module

| Pinn  | umber                                  |               |      | Timers |             |                |        | Communic        | oation Inter                                  | 2000 |        |   | Analogs |                                                  |         | HMI                                              |       |

|-------|----------------------------------------|---------------|------|--------|-------------|----------------|--------|-----------------|-----------------------------------------------|------|--------|---|---------|--------------------------------------------------|---------|--------------------------------------------------|-------|

| OFNS6 | Power, System, Gook, Debug, CAC, VBATT | Į,            |      | 900    | _ops, Po EG |                |        | USBFS, CAN      |                                               |      |        |   |         | DAC12, OPAMP                                     | - СМУ   | odons                                            |       |

| 5     | §.                                     | link          | P407 | AGTICO | GPT         | GP             | RTCOUT | USB_VBUS        | CTS4_RTS4                                     | SDA0 | SSL83  | * | ADTRG0  | ă                                                | No.     | SEGH!                                            | TS3   |

|       |                                        |               |      |        |             |                |        |                 |                                               |      |        |   |         |                                                  |         |                                                  |       |

| 2     | VSS_USB                                |               |      |        |             |                |        |                 |                                               |      |        |   |         |                                                  |         |                                                  |       |

| 3     |                                        |               | P915 | +      |             |                |        | USB_DM          |                                               |      |        |   |         |                                                  |         |                                                  |       |

| 4     |                                        |               | P914 | +      |             |                |        | USB_DP          |                                               |      |        |   |         |                                                  |         |                                                  |       |

| 5     | VCC_USB                                |               |      | +      |             |                |        |                 |                                               |      |        |   |         |                                                  |         |                                                  |       |

| 6     | VCC_USB                                |               |      | +      |             |                |        |                 |                                               |      |        |   |         |                                                  |         |                                                  |       |

| 7     |                                        | RQO           | P206 | +      | атш         |                |        | USB_VBUS<br>EN  | RXDA/<br>MISOA/SOL4                           | SDA1 | SSLB1  |   |         |                                                  |         | SEG12                                            | TS1   |

| ā     | CLXIDUT                                | RO1           | P208 | AGTO1  | GTIV        | GTIOCHA        |        | USB_OVRC<br>URA | TXDA/<br>MOSIA/<br>SDAA/<br>CTS9_RTS9         | SCL1 | SSLBO  |   |         |                                                  |         | SEG20                                            | TSCAP |

| 9     | CACREF                                 |               | P204 | AGTOI  | GTIW        | апос4в         |        | USB_OVRC        | SCK4/SCK9                                     | SCLO | RSPCKB |   |         |                                                  |         | 5EG23                                            | TSO   |

|       |                                        |               |      |        |             |                |        | URB             |                                               |      |        |   |         |                                                  |         |                                                  |       |

| 10    | RES                                    |               |      |        |             |                |        |                 |                                               |      |        |   |         |                                                  |         |                                                  |       |

| 11    | MD                                     |               | P201 |        |             |                |        |                 |                                               |      |        |   |         |                                                  |         |                                                  |       |

| 12    |                                        | NMI           | P200 |        |             |                |        |                 |                                               |      |        |   |         |                                                  |         |                                                  |       |

| 13    | TCK/<br>SWCLK                          |               | P300 |        | GTOUUP      | GTICCGA        |        |                 |                                               |      | SSLB1  |   |         |                                                  |         |                                                  |       |

| 14    | TMS/<br>SWDIO                          |               | P108 |        | GTOULO      | спосов         |        |                 | CTS9_RTS9<br>/SS9                             |      | SSLBO  |   |         |                                                  |         |                                                  |       |

| 15    | TDO/<br>SWO/<br>CLKOUT                 |               | P109 |        | GTOVUP      | GTIOCIA        |        | стхо            | SCK1/<br>TXD9/<br>MOSIS/<br>SDA9              |      | MOSIB  |   |         |                                                  |         | SEGSE                                            | TS10  |

| 16    | TDI                                    | RQ3           | P110 |        | GTOVLO      | стоств         |        | CRXXX           | RXD9/<br>MISO9/SCL9                           |      | MISCE  |   |         |                                                  | VCOUT   | SEG53                                            |       |

| 17    |                                        | RQ4           | PHH  |        |             | GTIOCSA        |        |                 | SCHS                                          |      | RSPCKB |   |         |                                                  |         |                                                  | TS12  |

| 18    | voc                                    |               |      |        |             |                |        |                 |                                               |      |        |   |         |                                                  |         |                                                  |       |

| 19    | vss                                    |               |      | $\top$ |             |                |        |                 |                                               |      |        |   |         |                                                  |         |                                                  |       |

| 20    |                                        | KR07          | P107 | 1      |             | GTIOCEA        |        |                 |                                               |      |        |   |         |                                                  |         | COMS                                             |       |

| 21    |                                        | KR06          | P106 | +      |             | стосав         |        |                 |                                               |      | SSLA3  |   |         |                                                  |         | COM2                                             |       |

| 22    |                                        | KR05/<br>IRQ0 | P105 | +      | GTETRGA     | GTIOC1A        |        |                 |                                               |      | SSLA2  |   |         |                                                  |         | COMI                                             | T934  |

| 23    |                                        | KROW<br>RO1   | P104 | +      | GTETRGS     | <b>GTIOCIB</b> |        |                 | RXDO/<br>MISCO/SCLO                           |      | SSLA1  |   |         |                                                  |         | COMD                                             | TS13  |

| 24    |                                        | KR03          | P103 | +      | GTOWUP      | GTIOC2A        |        | стко            | CTSQ_RTS0<br>/SS0                             |      | SSLAD  |   | AN019   |                                                  | CMPREFI | VL4                                              |       |

| 25    |                                        | 10002         | P102 | AGTOO  | GTOWLO      | 0110028        |        | CRXX            | SCKD                                          |      | RSPCKA |   | ANGOO   | <del>                                     </del> | CMPINI  | <del>                                     </del> |       |

| 26    |                                        | IRO1          | P101 | AGTEED | GTETRGS     | STICCEA        |        |                 | TXDO/<br>MOSIO/<br>SDAO/<br>CTS1_RTS1<br>/SS1 | SDA1 | MOSIA  |   | ADTRGO  |                                                  | CMPREFO | VL2                                              |       |

| Pin number                                      |          |      | Tim      | erc |                |        |     | Communic   | oation Inter    | 2006     |       |    | Analogs |              |        | HMI   |          |

|-------------------------------------------------|----------|------|----------|-----|----------------|--------|-----|------------|-----------------|----------|-------|----|---------|--------------|--------|-------|----------|

| GFNSB<br>Power, System, Gock, Debug, CAC, VBATT | Informpt |      | No rotts | AGT | GPT_OPS, PO EG | GPT    | RTC | USBFS, CAN | 90              | <u> </u> | 5.    | RF | ADC14   | DAG12, OPAMP | ACMPLP | SLCDC | 10 may 1 |

|                                                 | 02       | P100 | AGTI     | 100 | GTETRGA        | апосва |     |            | MISCO/<br>SCLO/ | SCL1     | MISCA |    |         |              | CMPING | VL1   |          |

Table 3.1 Hardware specifications (1/2)

| Item                  | Description                                        | Remarks                                              |

|-----------------------|----------------------------------------------------|------------------------------------------------------|

| Board size            | MCU Board                                          | MCU Board + Emulator Board                           |

|                       | 40.0 × 45.5[mm]                                    | 40 × 60[mm] (Include slit)                           |

|                       | Emulator Board                                     |                                                      |

|                       | 40.0 × 13.5[mm]                                    |                                                      |

| Power supply          | USB bus power (VBUS) 5V                            |                                                      |

| MCU                   | RENESAS                                            | Max. operating frequency: 100MHz                     |

|                       | R7FA4M2AD3CFL                                      | Arm Cortex-M33 core                                  |

|                       |                                                    | Code flash: 512KB                                    |

|                       |                                                    | Data flash: 8KB                                      |

|                       |                                                    | <ul> <li>SRAM: 128KB</li> </ul>                      |

|                       |                                                    | <ul> <li>48pin LQFP package (0.5mm pitch)</li> </ul> |

|                       |                                                    | Operating temperature: -40°C to<br>105°C             |

| Internal power supply | Circuit voltage: 3.3V                              | Output current : 150mA max                           |

|                       | LDO IC: RENESAS ISL9003A                           |                                                      |

| Clock                 | MCU main clock                                     |                                                      |

|                       | High-speed on-chip oscillator                      |                                                      |

|                       | MCU sub clock                                      |                                                      |

|                       | 32.768kHz crystal                                  |                                                      |

| MIC                   | CUI DEVICES                                        | Electret condenser microphone                        |

|                       | CMEJ-0415-42-LP                                    | Omni-directional                                     |

|                       |                                                    | Sensitivity: -42dBV/Pa                               |

|                       |                                                    | MIC2 is optional.                                    |

| MIC AMP               | Amp Gain:                                          | Amplifier gain can be changed by                     |

|                       | <ul> <li>46dB(201 times), Default value</li> </ul> | replacing the external resistor.                     |

|                       | OPAMP IC:                                          |                                                      |

|                       | RENESAS READ2303G                                  |                                                      |

| LED                   | Power LED:                                         |                                                      |

|                       | orange color × 1 pc                                |                                                      |

|                       | Function display:                                  | MCU port control                                     |

|                       | 3-color (RGB) LED × 1 pc                           |                                                      |

| Switch                | System reset switch                                | Push switch × 1 pc                                   |

|                       | Mode switch                                        | DIP switch × 1 bit                                   |

| USB connector         | USB Micro B × 1 pc                                 | USB2.0 full speed                                    |

| Emulator connector    | J-Link 9-pin Cortex-M adopter × 1 pc               |                                                      |

| PMOD connector        | 2.54mm pitch,12 pin                                | Optional                                             |

|                       | (6pin × 2) × 1 pc                                  |                                                      |

| Pin ni | ımber  |                                             |           |         | Timore |                                                  |               |                                                  | Communi    | oation inter  | 3006                                             |       |                                                  | Analogs |             |        | HMI    |      |

|--------|--------|---------------------------------------------|-----------|---------|--------|--------------------------------------------------|---------------|--------------------------------------------------|------------|---------------|--------------------------------------------------|-------|--------------------------------------------------|---------|-------------|--------|--------|------|

| OFNSE  |        | rower, oystem, coors, bedog, circ., yakii i | Informati | apod Qi |        | T_OPS, PO EG                                     | <u>-</u>      | 9                                                | USBFS, CAN | _             |                                                  |       |                                                  | ADC14   | DAC12 OPAMP | ACMPLP | SLCDC  | CIBU |

|        | XCIN   | 2                                           |           | P215    | AGT    | PP.                                              | GPT           | P. C                                             | S          | 8             | 2                                                | 5     | 2                                                | ΑD      | ď           | ¥      | ल      | 5    |

|        | ALUM . |                                             |           | -213    | 1      | 1                                                |               |                                                  |            |               |                                                  |       | 1                                                |         |             |        |        |      |

| 50     | NOOUT  | 1                                           |           | P214    |        |                                                  |               |                                                  |            |               |                                                  |       |                                                  |         |             |        |        |      |

| 51     | vss    | +                                           | $\neg$    |         | +      | <del>                                     </del> |               | <del>                                     </del> |            |               | <del>                                     </del> |       | <del>                                     </del> |         |             |        |        |      |

| 52     | XTAL.  | RQ2                                         | _         | P213    |        | GTETRGA                                          | GTIOCGA       | <u> </u>                                         |            | TXDW          | <u> </u>                                         | -     | -                                                | _       |             |        |        |      |

| _      |        |                                             |           |         | 1      |                                                  |               |                                                  |            | MOSH/<br>SDA1 |                                                  |       |                                                  |         |             |        |        |      |

| 53     | EXTAL  | RQ3                                         |           | P212    | AGTEE1 | GTETRGS                                          | <b>стосов</b> |                                                  |            | RXD1/         |                                                  |       | -                                                |         |             |        |        |      |

| 54     | voc    | +-                                          | -         |         | +-     | -                                                |               | <del>                                     </del> |            | MISO1/SCL1    |                                                  |       | -                                                |         |             |        |        |      |

|        |        | $\perp$                                     |           |         |        |                                                  |               |                                                  |            |               |                                                  |       |                                                  |         |             |        |        |      |

| 55     |        | ROS                                         |           | P414    |        |                                                  | апосав        |                                                  |            |               |                                                  | SSLA1 | RF                                               |         |             |        |        |      |

|        |        | ROS                                         | _         | P400    | +      | CHOWUP                                           | GHIOCEA       |                                                  | USB_EXICE  |               | $\vdash$                                         | -     | +                                                |         |             | _      | MEMORI |      |

#### Noted:

Not all of MCU pin be connected for Module use . User have to check output pin of module and check pin function which corresponding.

Guinea Tech.

To be available

Module Picture

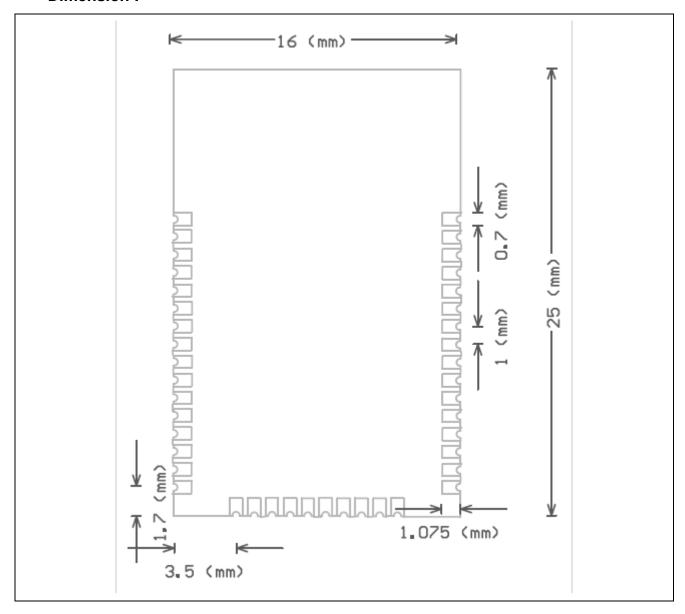

## Dimension:

#### 3. Characteristics:

#### 3.1 BLE Characteristics:

Transmission Characteristics:

Conditions: VCC=VCC\_RF=AVCC\_RF=3,3V, VSS=VSS\_RF=0V, Ta=25°C

| Parameter                  | Symbol                  | Min  | Тур | Max  | Unit | Test conditions   |

|----------------------------|-------------------------|------|-----|------|------|-------------------|

| Range of frequency         | RF <sub>CF</sub>        | 2402 | -   | 2480 | MHz  |                   |

| Data rate                  | RF <sub>DATA_2M</sub>   | -    | 2   | -    | Mbps |                   |

|                            | RF <sub>DATA_1M</sub>   | -    | 1   | -    | Mbps |                   |

|                            | RF <sub>DATA_500k</sub> | -    | 500 | -    | kbps |                   |

|                            | RF <sub>DATA_125k</sub> | -    | 125 | -    | kbps |                   |

| Maximum transmitted output | RF <sub>POWER</sub>     | -    | 0   | 2    | dBm  | 0 dBm output mode |

| power                      |                         | -    | 4   | 6    | dBm  | 4 dBm output mode |

| Output frequency error     | RF <sub>TXFERR</sub>    | -10  | -   | 10   | ppm  | *1                |

Note: The characteristics are based on pins and functions other than those for the BLE interface not being in use.

Note 1. This does not take frequency errors due to manufacturing irregularities, drift with temperature, or deterioration of the crystal over time into account.

Reception Characteristics(1Mbps)

Conditions: VCC=VCC\_RF=AVCC\_RF=3,3V, VSS=VSS\_RF=0V, Ta=25°C

| Item                             | Symbol                 | Min. | Тур. | Max.       | Unit | Test Conditions  |                    |  |

|----------------------------------|------------------------|------|------|------------|------|------------------|--------------------|--|

| Input frequency                  | RF <sub>RXFIN_1M</sub> | 2402 | _    | 2480       | MHz  |                  |                    |  |

| Maximum input level              | RF <sub>LEVL_1M</sub>  | -10  | 4    | _          | dBm  | *1               |                    |  |

| Receiver sensitivity             | RF <sub>STY_1M</sub>   | _    | -95  | _          | dBm  | *1               |                    |  |

| Secondary emission strength      | RF <sub>RXSP_1M</sub>  | _    | -72  | -57        | dBm  | 30MHz to 1GHz    |                    |  |

|                                  |                        | _    | -54  | -47        | dBm  | 1GHz to 12GHz    |                    |  |

| Co-channel rejection ratio       | RF <sub>CCR_1M</sub>   | _    | -7   | _          | dB   | Prf = -67dBm*1   |                    |  |

| Adjacent channel rejection ratio | RF <sub>ADCR_1M</sub>  | _    | -1   | _          | dB   | Prf = -67dBm*1   | ±1MHz              |  |

|                                  |                        | _    | 34   | _          | dB   |                  | ±2MHz              |  |

|                                  |                        | _    | 35   | _          | dB   |                  | ±3MHz              |  |

| Blocking                         | RF <sub>BLK_1M</sub>   | _    | 0    | _          | dBm  | Prf = -67dBm*1   | 30MHz to 2000MHz   |  |

|                                  |                        | _    | -24  | _          | dBm  |                  | 2000MHz to 2399MHz |  |

|                                  |                        | _    | -20  | _          | dBm  |                  | 2484MHz to 3000MHz |  |

|                                  |                        | _    | -4   | _          | dBm  | 7                | > 3000MHz          |  |

| Allowable frequency deviation*2  | RF <sub>RXFER_1M</sub> | -120 | _    | 120        | ppm  | *1               | •                  |  |

| RSSI accuracy                    | RF <sub>RSSIS_1M</sub> | -    | ±4   | <b> </b> _ | dB   | -70dBm ≤ Prf ≤ - | -10dBm             |  |

Note: The characteristics are based on pins and functions other than those for the BLE interface not being in use.

Note 1. PER ≤ 30.8%, and a 37-byte payload

Note 2. Allowable range of difference between the center frequency for the RF input signals and the carrier frequency generated within the chip

Conditions: VCC=VCC\_RF=AVCC\_RF=3,3V, VSS=VSS\_RF=0V , Ta=25  $^{\circ}\text{C}$

| Item                             | Symbol                   | Min. | Тур. | Max.       | Unit | Test Conditions  |                    |  |

|----------------------------------|--------------------------|------|------|------------|------|------------------|--------------------|--|

| Input frequency                  | RF <sub>RXFIN_500k</sub> | 2402 | _    | 2480       | MHz  |                  |                    |  |

| Maximum input level              | RF <sub>LEVL_500k</sub>  | -10  | 4    | _          | dBm  | *1               |                    |  |

| Receiver sensitivity             | RF <sub>STY_500k</sub>   | _    | -100 | _          | dBm  | *1               |                    |  |

| Secondary emission strength      | RF <sub>RXSP_500k</sub>  | _    | -72  | -57        | dBm  | 30MHz to 1GHz    |                    |  |

|                                  |                          | _    | -54  | <b>-47</b> | dBm  | 1GHz to 12GHz    |                    |  |

| Co-channel rejection ratio       | RF <sub>CCR_500k</sub>   | _    | -4   | _          | dB   | Prf = -72dBm*1   |                    |  |

| Adjacent channel rejection ratio | RF <sub>ADCR_500k</sub>  | _    | 6    | _          | dB   | Prf = -72dBm*1   | ±1MHz              |  |

|                                  |                          | _    | 36   | _          | dB   | ]                | ±2MHz              |  |

|                                  |                          | _    | 42   | _          | dB   | ]                | ±3MHz              |  |

| Blocking                         | RF <sub>BLK_500k</sub>   | _    | 0    | _          | dBm  | Prf = -72dBm*1   | 30MHz to 2000MHz   |  |

|                                  |                          | _    | -23  | _          | dBm  | ]                | 2000MHz to 2399MHz |  |

|                                  |                          | _    | -20  | _          | dBm  | ]                | 2484MHz to 3000MHz |  |

|                                  |                          | _    | -7   | _          | dBm  | 1                | > 3000MHz          |  |

| Allowable frequency deviation*2  | RF <sub>RXFER_500k</sub> | -120 | _    | 120        | ppm  | *1               |                    |  |

| RSSI accuracy                    | RF <sub>RSSIS_500k</sub> | _    | ±4   | _          | dB   | -70dBm ≤ Prf ≤ - | -10dBm             |  |

Note: The characteristics are based on pins and functions other than those for the BLE interface not being in use.

Note 1. PER ≤ 30.8%, and a 37-byte payload

Note 2. Allowable range of difference between the center frequency for the RF input signals and the carrier frequency generated within the chip

Reception Characteristics (125 Kbps)

Conditions: VCC=VCC\_RF=AVCC\_RF=3,3V, VSS=VSS\_RF=0V , Ta=25  $^{\circ}\text{C}$

| Item                             | Symbol                   | Min. | Тур. | Max. | Unit | Test Conditions               |                      |  |

|----------------------------------|--------------------------|------|------|------|------|-------------------------------|----------------------|--|

| Input frequency                  | RF <sub>RXFIN_125k</sub> | 2402 | _    | 2480 | MHz  |                               |                      |  |

| Maximum input level              | RF <sub>LEVL_125k</sub>  | -10  | 4    | _    | dBm  | *1                            |                      |  |

| Receiver sensitivity             | RF <sub>STY_125k</sub>   | _    | -105 | _    | dBm  | *1                            |                      |  |

| Secondary emission strength      | RF <sub>RXSP_125k</sub>  | _    | -72  | -57  | dBm  | 30 MHz to 1 GHz               |                      |  |

|                                  |                          | _    | -54  | -47  | dBm  | 1 GHz to 12 GHz               |                      |  |

| Co-channel rejection ratio       | RF <sub>CCR_125k</sub>   | _    | -2   | _    | dB   | Prf = -79 dBm*1               |                      |  |

| Adjacent channel rejection ratio | RF <sub>ADCR_125k</sub>  | _    | 12   | _    | dB   | Prf = -79 dBm*1               | ±1 MHz               |  |

|                                  |                          | _    | 39   | _    | dB   |                               | ±2 MHz               |  |

|                                  |                          | _    | 45   | _    | dB   |                               | ±3 MHz               |  |

| Blocking                         | RF <sub>BLK_125k</sub>   | _    | 0    | _    | dBm  | Prf = -79 dBm*1               | 30 MHz to 2000 MHz   |  |

|                                  |                          | _    | -23  | _    | dBm  |                               | 2000 MHz to 2399 MHz |  |

|                                  |                          | _    | -20  | _    | dBm  |                               | 2484 MHz to 3000 MHz |  |

|                                  |                          | _    | -1   | _    | dBm  |                               | > 3000MHz            |  |

| Allowable frequency deviation*2  | RF <sub>RXFER_125k</sub> | -120 | _    | 120  | ppm  | *1                            |                      |  |

| RSSI accuracy                    | RF <sub>RSSIS_125k</sub> | _    | ±4   | _    | dB   | T <sub>a</sub> = +25°C, -70 ( | dBm ≤ Prf ≤ −10 dBm  |  |

Note: The characteristics are based on pins and functions other than those for the BLE interface not being in use.

Note 1. PER ≤ 30.8%, and a 37-byte payload

Note 2. Allowable range of difference between the center frequency for the RF input signals and the carrier frequency generated within the chip

Bluetooth low Energy operating and stanby current

Conditions: VCC=VCC\_RF=AVCC\_RF=3,3V, VSS=VSS\_RF=0V , Ta=25  $^{\circ}\text{C}$

|                          |                                         |            |     |       | yp<br>utput power | 4          |       |                    |

|--------------------------|-----------------------------------------|------------|-----|-------|-------------------|------------|-------|--------------------|

| Dt                       |                                         | C          |     |       | <del> </del>      | -  <b></b> | 11-34 | Test<br>conditions |

| Parameter                | 1                                       | Symbol     | Min | 0 dBm | 4 dBm             | Max        | Unit  |                    |

| BLE operating<br>current | Transmit mode, 2 Mbps                   | ldd_tx     | -   | 4.5   | 8.7               | -          | mA    | -                  |

| (When DC-DC              | Transmit mode, 1 Mbps                   |            | -   |       |                   | -          | mA    | -                  |

| converter is             | Transmit mode, 500 kbps                 |            | -   |       |                   | -          | mA    | -                  |

| selected)                | Transmit mode, 125 kbps                 |            | -   |       |                   | -          | mA    | -                  |

|                          | Receive mode, 2 Mbps<br>Prf = -67 dBm   | ldd_rx     | -   | 3.3   | 3.5               | -          | mA    | -                  |

|                          | Receive mode, 1 Mbps<br>Prf = -67 dBm   | ]          | -   |       |                   | -          | mA    | -                  |

|                          | Receive mode, 500 kbps<br>Prf = -72 dBm | ]          | -   |       |                   | -          | mA    | -                  |

|                          | Receive mode, 125 kbps<br>Prf = -79 dBm |            | -   |       |                   | -          | mA    | -                  |

|                          | Idle mode                               | ldd_idle - |     | C     | ).5               | -          | mA    | -                  |

|                          | Deep sleep mode                         | ldd_slp    | -   | 1.5   |                   | -          | μА    | -                  |

|                          | Power down mode                         | ldd_down - |     | 0.1   |                   | -          | μА    | -                  |

| BLE operating            | Transmit mode, 2 Mbps                   | ldd_tx     | -   | 10.2  | 18.1              | -          | mA    | -                  |

| current<br>(When linear  | Transmit mode, 1 Mbps                   | 1          | -   |       |                   | -          | mA    | -                  |

| regulator is             | Transmit mode, 500 kbps                 | 1          | -   |       |                   | -          | mA    | -                  |

| selected)                | Transmit mode, 125 kbps                 | 1          | -   |       |                   | -          | mA    | -                  |

|                          | Receive mode, 2M bps<br>Prf = -67 dBm   | ldd_rx     | -   | 6     | 3.9               | -          | mA    | -                  |

|                          | Receive mode, 1 Mbps<br>Prf = -67 dBm   | ]          | -   | 6     | 3.9               | -          | mA    | -                  |

|                          | Receive mode, 500 kbps<br>Prf = -72 dBm |            | -   | 6     | 3.9               | -          | mA    | -                  |

|                          | Receive mode, 125 kbps<br>Prf = -79 dBm | ]          | -   | 7     | 7.1               | -          | mA    | -                  |

|                          | ldd_idle                                | ldd_idle   | -   | 0     | ).7               | -          | mA    | -                  |

|                          | ldd_slp                                 | ldd_slp    | -   | 1     | 1.5               | -          | μA    | -                  |

|                          | ldd down                                | ldd down   | -   | 0     | 0.1               | -          | μА    | -                  |

## 3.2 MCU Characteristics:

MCU operating and standby current

Conditions: VCC=AVCC0=1.8 to 3.6V

| Parameter |            |                                                   |                                                                |               | Symbol | Typ*10 | Max  | Unit | Test<br>conditions |

|-----------|------------|---------------------------------------------------|----------------------------------------------------------------|---------------|--------|--------|------|------|--------------------|

| Supply    | High-speed | Normal mode                                       | All peripheral clock                                           | ICLK = 48 MHz | Icc    | 8.4    | -    | mA   | *7                 |

| urrent*1  | mode*2     |                                                   | disabled, while (1) code<br>executing from flash*5             | ICLK = 32 MHz |        | 5.9    | -    | 1    |                    |

|           |            |                                                   |                                                                | ICLK = 16 MHz |        | 3.5    | -    | Ī    |                    |

|           |            |                                                   |                                                                | ICLK = 8 MHz  |        | 2.3    | -    | 1    |                    |

|           |            |                                                   | All peripheral clock                                           | ICLK = 48 MHz |        | 17.9   | -    | Ī    |                    |

|           |            |                                                   | disabled, CoreMark code<br>executing from flash*5              | ICLK = 32 MHz |        | 12.4   | -    | Ī    |                    |

|           |            |                                                   | ICLK = 16 MHz                                                  |               | 7.0    | -      | 1    | *8   |                    |

|           |            |                                                   | ICLK = 8 MHz                                                   |               | 4.3    | -      | Ī    |      |                    |

|           |            | All peripheral clock                              | ICLK = 48 MHz                                                  |               | 21.2   | -      | Ī    |      |                    |

|           |            | enabled, while (1) code<br>executing from flash*5 | ICLK = 32 MHz                                                  |               | 16.0   | -      |      |      |                    |

|           |            |                                                   | ICLK = 16 MHz                                                  |               | 8.8    | -      |      |      |                    |

|           |            |                                                   |                                                                | ICLK = 8 MHz  |        | 5.1    | -    | 1    |                    |

|           |            |                                                   | All peripheral clock<br>enabled, code executing<br>from SRAM*5 | ICLK = 48 MHz |        | -      | 56.0 |      | *9                 |

|           |            | Sleep mode                                        | All peripheral clock                                           | ICLK = 48 MHz |        | 3.7    | -    | 1    | *7                 |

|           |            |                                                   | disabled*5                                                     | ICLK = 32 MHz |        | 2.7    | -    | Ī    |                    |

|           |            |                                                   |                                                                | ICLK = 16 MHz |        | 2.0    | -    | 1    |                    |

|           |            |                                                   |                                                                | ICLK = 8 MHz  |        | 1.5    | -    | Ī    |                    |

|           |            |                                                   | All peripheral clock                                           | ICLK = 48 MHz |        | 16.4   | -    | Ī    | *9                 |

|           |            |                                                   | enabled*5                                                      | ICLK = 32 MHz |        | 12.7   | -    | †    | *8                 |

|           |            |                                                   |                                                                | ICLK = 16 MHz |        | 7.2    | -    | †    |                    |

|           |            |                                                   |                                                                | ICLK = 8 MHz  |        | 4.3    | -    | †    |                    |

|           |            | Increase during                                   | BGO operation*6                                                |               | ┑      | 2.5    | -    | 1    | -                  |

Guinea Tech.

| Middle-speed | Normal mode     | All peripheral clock                               | ICLK = 12 MHz | Icc | 2.5<br>2.1<br>1.0<br>5.2 | -    | mA | *7 |

|--------------|-----------------|----------------------------------------------------|---------------|-----|--------------------------|------|----|----|

| mode*2       |                 | disabled, while (1) code<br>executing from flash*5 | ICLK = 8 MHz  |     | 2.1                      | -    | 1  |    |

|              |                 |                                                    | ICLK = 1 MHz  |     | 1.0                      | -    | 1  |    |

|              |                 | All peripheral clock                               | ICLK = 12 MHz |     | 5.2                      | -    | 1  |    |

|              |                 | disabled, CoreMark code<br>executing from flash*5  | ICLK = 8 MHz  |     | 4.0                      | -    | 1  |    |

|              |                 |                                                    | ICLK = 1 MHz  | 7   | 1.3                      | -    | Ī  | *8 |

|              |                 | All peripheral clock                               | ICLK = 12 MHz |     | 6.5                      | -    | 1  |    |

|              |                 | ICL                                                | ICLK = 8 MHz  |     | 4.8                      | -    |    |    |

|              |                 |                                                    | ICLK = 1 MHz  |     | 1.6                      | -    |    |    |

|              |                 |                                                    | ICLK = 12 MHz |     | -                        | 23.0 |    |    |

|              | Sleep mode      | All peripheral clock                               | ICLK = 12 MHz |     | 1.4                      | -    | -  | *  |

|              |                 | disabled*5                                         | ICLK = 8 MHz  |     | 1.3 -                    | 1    |    |    |

|              |                 |                                                    | ICLK = 1 MHz  |     | 0.9                      | -    | 7  |    |

|              |                 | enabled*5                                          | ICLK = 12 MHz |     | 5.3<br>4.0<br>1.5        | -    | 1  | *8 |

|              |                 |                                                    | ICLK = 8 MHz  |     |                          | -    | 1  |    |

|              |                 |                                                    | ICLK = 1 MHz  |     |                          | -    | 1  |    |

|              | Increase during | BGO operation*6                                    | •             |     | 2.5                      | -    | 1  | -  |

| Parameter           |                       |             |                                                                            |              | Symbol | Typ*10 | Max | Unit | Test<br>conditions |

|---------------------|-----------------------|-------------|----------------------------------------------------------------------------|--------------|--------|--------|-----|------|--------------------|

| Supply<br>current*1 | Low-speed<br>mode*3   | Normal mode | All peripheral clock<br>disabled, while (1) code<br>executing from flash*5 | ICLK = 1 MHz | lcc    | 0.4    | -   | mA   | *7                 |

|                     |                       |             | All peripheral clock<br>disabled, CoreMark code<br>executing from flash*5  | ICLK = 1 MHz |        | 0.6    | -   |      |                    |

|                     |                       |             | All peripheral clock<br>enabled, while (1) code<br>executing from flash*5  | ICLK = 1 MHz |        | 1.1    | -   |      | *8                 |

|                     |                       |             | All peripheral clock<br>enabled, code executing<br>from SRAM*5             | ICLK = 1 MHz |        | -      | 2.5 |      |                    |

|                     |                       | Sleep mode  | All peripheral clock disabled*5                                            | ICLK = 1 MHz |        | 0.3    | -   | 1    | *7                 |

|                     |                       |             | All peripheral clock enabled*5                                             | ICLK = 1 MHz |        | 1.0    | -   |      | *8                 |

|                     | Low-voltage<br>mode*3 | Normal mode | All peripheral clock<br>disabled, while (1) code<br>executing from flash*5 | ICLK = 4 MHz | Icc    | 1.8    | -   | mA   | *7                 |

|                     |                       |             | All peripheral clock<br>disabled, CoreMark code<br>executing from flash*5  | ICLK = 4 MHz |        | 3.0    | -   |      |                    |

|                     |                       |             | All peripheral clock<br>enabled, while (1) code<br>executing from flash*5  | ICLK = 4 MHz |        | 3.3    | -   |      | *8                 |

|                     |                       |             | All peripheral clock<br>enabled, code executing<br>from SRAM*5             | ICLK = 4 MHz |        | -      | 9.0 |      |                    |

|                     |                       | Sleep mode  | All peripheral clock disabled*5                                            | ICLK = 4 MHz |        | 1.4    | -   | 1    | *7                 |

|                     |                       |             | All peripheral clock enabled*5                                             | ICLK = 4 MHz |        | 2.9    | -   | 1    | *8                 |

Guinea Tech. GDS-B5I

| L                          | ı           | I                                                                          | I                 | i   | ı    | 1     |    | 1  |

|----------------------------|-------------|----------------------------------------------------------------------------|-------------------|-----|------|-------|----|----|

| Subosc-<br>speed<br>mode*4 | Normal mode | All peripheral clock<br>disabled, while (1) code<br>executing from flash*5 | ICLK = 32.768 kHz | Icc | 9.3  | -     | μА | *8 |

|                            |             | All peripheral clock<br>enabled, while (1) code<br>executing from flash*5  | ICLK = 32.768 kHz |     | 17.2 |       |    |    |

|                            |             | All peripheral clock<br>enabled, code executing<br>from SRAM*5             | ICLK = 32.768 kHz |     | -    | 106.0 |    |    |

|                            | Sleep mode  | All peripheral clock disabled*5                                            | ICLK = 32.768 kHz |     | 6.0  |       |    |    |

|                            |             | All peripheral clock enabled*5                                             | ICLK = 32.768 kHz |     | 14.0 | -     |    |    |

- Note 1. Supply current values do not include output charge/discharge current from all pins. The values apply when internal pull-up MOSs are in the off state.

- Note 2. The clock source is HOCO.

- Note 3. The clock source is MOCO.

- Note 4. The clock source is the sub-clock oscillator.

- Note 5. This does not include BGO operation.

- Note 6. This is the increase for programming or erasure of the flash memory for data storage during program execution.

- Note 7. FCLK, PCLKB, PCLKC and PCLKD are set to divided by 64.

Note 8. FCLK, PCLKB, PCLKC and PCLKD are the same frequency as that of ICLK.

Note 9. FCLK and PCLKB are set to divided by 2 and PCLKA, PCLKC and PCLKD are the same frequency as that of ICLK.

- Note 10. VCC = 3.3 V.