# OSA-79G-AL Radar Sensor Reference Guide

Forward Collision Warning (FCW) Application

# TABLE OF CONTENTS

| Introduction                              |   |

|-------------------------------------------|---|

| Package Contents                          |   |

| Hardware                                  |   |

| installation                              |   |

| Testing                                   |   |

| Technical Specifications                  |   |

| Specifications                            |   |

| Standards                                 | 7 |

| Appendix                                  | 8 |

| UART Cable Connector Pin-out              |   |

| General Input/Output Port Characteristics |   |

| Output Voltage Characteristics            |   |

## INTRODUCTION

The 79 GHz Radar Sensor uses Frequency-Modulated Continuous-Wave (FMCW) radar technology to detect whether there are moving objects in the areas around the vehicle that cannot be directly observed by the driver. These areas are called blind spot areas around the vehicle.

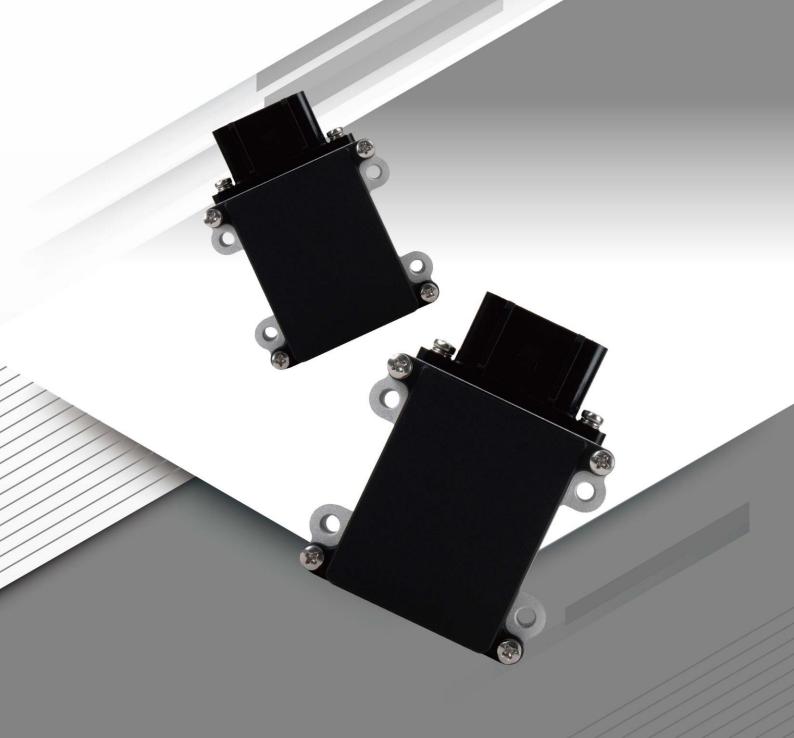

## **PACKAGE CONTENTS**

The following items should be included in the packaging:

- 79 GHz Radar Sensor

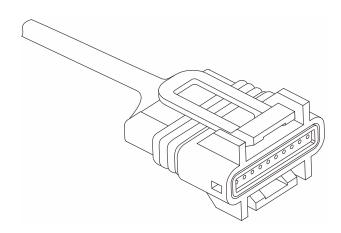

- UART cable with a 10-pin connector

- Mounting accessories

NOTE: If any of the items, mentioned above, is not included in the packaging or are damaged in any way, contact your reseller immediately.

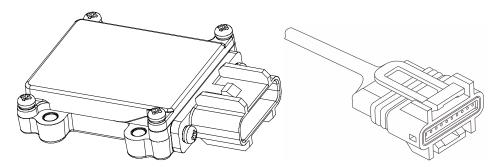

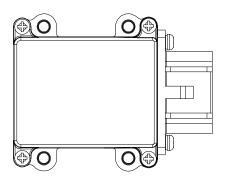

## **HARDWARE**

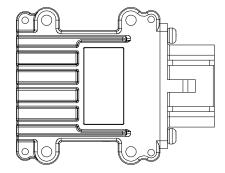

The front and back panels of the radar sensor consist of different materials. The following diagrams will illustrate the front and back view of the radar sensor:

**Back Panel** - The back panel is made from metal. Metal will prevent the radar signal from reaching the inside of the vehicle.

# **INSTALLATION**

In this section, we'll discuss the successful installation of the radar sensor onto the rear corners of most vehicles.

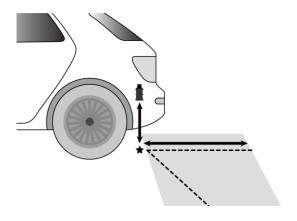

- ① Unbox the radar sensor and remove the rear bumper from the vehicle.

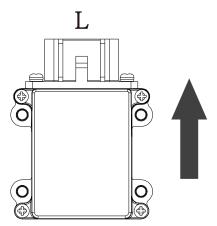

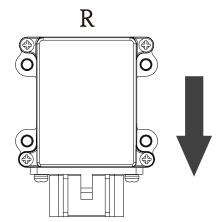

- 2 The radar sensor can be installed onto the rear-left and/or rear-right corner of the vehicle with the metal side facing the vehicle.

- When the radar sensor is installed onto the rear-left corner of the vehicle, the cable should be facing upwards.

When the radar sensor is installed onto the rear-right corner of the vehicle, the cable should be facing downwards.

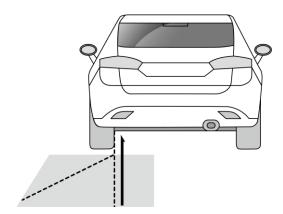

- 3 The radar sensors should be installed facing backwards with:

- The left-rear sensor rotated clockwise by 25 degrees.

- The right-rear sensor rotated anti-clockwise by 25 degrees.

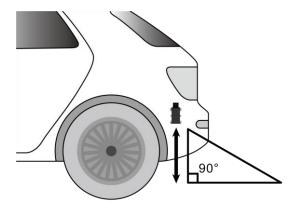

- 4 The radar sensor should be mounted onto the vehicle at a 90-degree angle, perpendicular to the ground.

Horizontal Angle ( $\theta$ 1,  $\theta$ 2): 25 degrees ( $\pm$ 3 degrees)

Vertical Angle: 90 degrees (±3 degrees)

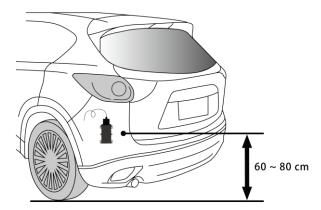

(5) The radar sensor should be mounted onto the vehicle between 60 cm and 80 cm from the ground.

(6) When installation and testing are complete, the bumper can be re-installed onto the vehicle. The space between the bumper and the radar sensor must be at least 1 cm wide. No electronic/electric products or equipment that contain metal should be between the radar sensor and the area of detection.

#### **TESTING**

In this section, we'll discuss how to test/calibrate the radar sensor to ensure that the radar sensor is working properly. An object, containing metal, with a height of at least 120 cm and a diameter of at least 21 cm, can be used to test the range and reliability of the radar detection area. A good example of an object that can be used for testing is a plastic pipe/tube wrapped with aluminum foil.

**NOTE:** Radar detection is based on movement. The person that moves the testing object should stand in-line with the object for more accurate test results.

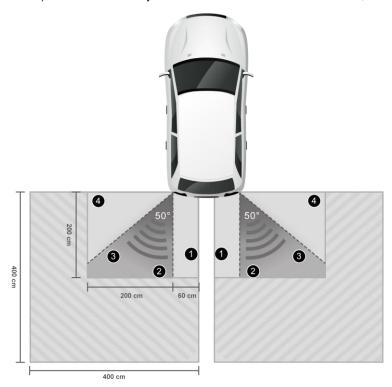

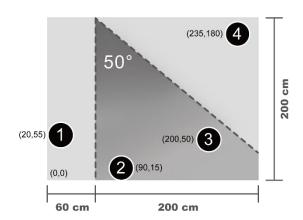

Two test areas (each 400 cm by 400 cm) should cleared of any obstacles at the rear corners of the vehicle, as shown in the following diagram:

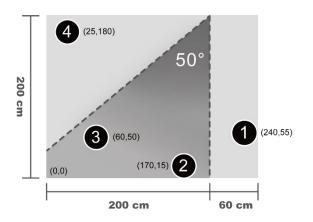

The detection area of the radar sensor, operating in 'Mode 1', is 200 cm by 200 cm. With an operating angle of 50 degrees, the true shape of the detection area will be more triangular than rectangular, as indicated in the diagram above. For practical purposes, let's refer to the triangular detection area as the **real detection area**.

Starting from the bottom left corner (0 cm, 0cm); measure and mark out the following positions that will be used in the test:

#### Left-rear corner:

- **Position •**: 240 cm from the left, 55 cm from the bottom

- Position 2: 170 cm from the left, 15 cm from the bottom

- Position **3**: 60 cm from the left, 50 cm from the bottom

- Position 4: 25 cm from the left, 180 cm from the bottom

#### Right-rear corner:

- Position ●: 20 cm from the left, 55 cm from the bottom

- Position **2**: 90 cm from the left, 15 cm from the bottom

- Position **⑤**: 200 cm from the left, 50 cm from the bottom

- Position 4: 235 cm from the left, 180 cm from the bottom

- When the test metal object is placed on positions and •, the radar sensor should not detect an obstruction.

- When the test metal object is placed on positions ② and ③, the radar sensor should detect an obstruction.

In the diagrams below, the closest corner of the real detection area (triangular shape) will start **right below** the radar sensor and **in-line** with the **inside edge** of the **closest wheel** on the vehicle.

The operation "Mode" can be specified through the UART interface using terminal software like "PuTTY". The default mode is Mode 1.

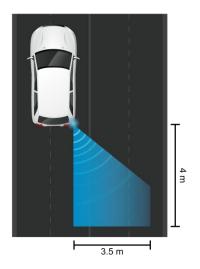

The three modes that can be specified are:

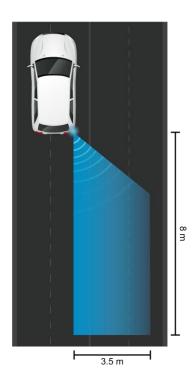

Mode "1" (BSD) - This mode is used to detect Mode "2" (LCA1) - This mode is used to vehicles, overtaking/passing our vehicle from behind, from 4 meters back, between the speeds of 30~50 km/h. The maximum width right/left is one lane wide.

from behind, from 8 meters back, between the from behind, from 12 meters back, between speeds of 50~80 km/h. The maximum width right/left is one lane wide.

Mode "3" (LCA2) - This mode is used to detect vehicles, overtaking/passing our vehicle detect vehicles, overtaking/passing our vehicle the speeds of 80 km/h and above. The maximum width right/left is one lane wide.

# **TECHNICAL SPECIFICATIONS**

# **SPECIFICATIONS**

| PHYSICAL & HARDWARE     |                                 |                          |                            |  |  |

|-------------------------|---------------------------------|--------------------------|----------------------------|--|--|

| Dimensions (L x W x H)  | 78.3 mm x 61.8 mm x 19.8 mm     | Weight                   | ?? kg                      |  |  |

| Housing Material (Rear) | Metal                           | Housing Material (Front) | Plastic                    |  |  |

| Material (Housing)      | ??? PC (UL94v2)                 | Material Body            | ??? Plastic/Metal          |  |  |

| Chipset                 | TI AWR1642                      | On-Chip Memory           | 1.5 MB                     |  |  |

| Power                   |                                 |                          |                            |  |  |

| Supply Voltage          | 12 VDC                          | Max. Power Consumption   | 8 Watts                    |  |  |

| RADAR SIGNAL            |                                 |                          |                            |  |  |

| Frequency Range         | 78 GHz to 81 GHz                | Signal Range             | Between 0.5 and 180 meters |  |  |

| FOV (Horizontal)        | 60 degrees                      | FOV (Vertical)           | 30 degrees                 |  |  |

| TX Power                | 12.5 dBm                        | RX Noise Figure          | 14 dB (76 to 79 GHz)       |  |  |

| Channels                | Receive 4, Transmit 2           | Phase Noise at 1 MHz     | - 95 dBc/Hz (76 to 79 GHz) |  |  |

| ENVIRONMENT             |                                 |                          |                            |  |  |

| Operating Temperature   | -40°C to 85°C                   | Storage Temperature      | -??°C to ??°C              |  |  |

| Operating Humidity      | 10% to 90% (Non-condensing)     | Storage Humidity         | 0% to 95% (Non-condensing  |  |  |

| CONNECTOR & CABLE       |                                 |                          |                            |  |  |

| Cable Length            | ??? centimeters/meters          | Cable Type               | ??? RG 316D                |  |  |

| Cable Color             | ???                             | Connector Pinout         | See <u>here</u>            |  |  |

| INTERFACE & SOFTWARE    |                                 |                          |                            |  |  |

| Host Interface          | CAN (Two instances, 1 x CAN-FD) | - Built-in Firmware ROM  |                            |  |  |

| ADC Channels            | Up to 6                         | SPI Channels             | Up to 2                    |  |  |

| UARTs                   | Up to 2                         | Other                    | I <sup>2</sup> C, GPIOs    |  |  |

# **S**TANDARDS

| STANDARD              | DESCRIPTION                                                       |  |  |  |

|-----------------------|-------------------------------------------------------------------|--|--|--|

| Regulatory Compliance | Comply with CE Markings per directives 2004/108/EC and 2006/95/EC |  |  |  |

|                       | FCC/IC Report Class A                                             |  |  |  |

|                       | UL/cUL Listed Mark                                                |  |  |  |

| Safety                | UL/CSA-C22.2 NO. 60950-1-07                                       |  |  |  |

| EMC                   | EN 55022/EN 55024, Class A                                        |  |  |  |

|                       | FCC CFR47, Part 15B, Class A                                      |  |  |  |

|                       | ICES-003, Class A                                                 |  |  |  |

| IEC Standard 60529    | IP67 to IP69K Compliance                                          |  |  |  |

| RoHS Directive        | ???                                                               |  |  |  |

| WEEE Directive        | ???                                                               |  |  |  |

# **A**PPENDIX

# **UART CABLE CONNECTOR PIN-OUT**

The following table lists the connector pin-out descriptions of the Universal Asynchronous Receiver-Transmitter (UART) cable:

| PIN NUMBER | Түре    | Color    | DESCRIPTION                                                           |  |

|------------|---------|----------|-----------------------------------------------------------------------|--|

| 1          | GND     | Black    | Pin used for the ground connection.                                   |  |

| 2          | 12 V    | Red      | Pin used for supplying 5 V power to the unit.                         |  |

| 3          | 12 V    | Dark Red | Pin used for supplying 5 V power to the unit.                         |  |

| 4          | CANL    | Yellow   | Controller Area Network Low (CANL) pin.                               |  |

| 5          | CANH    | Purple   | Controller Area Network High (CANH) pin.                              |  |

| 6          | GPIO 1  | Green    | General-Purpose Input/Output 1 (GPIO 1) pin.                          |  |

| 7          | GPIO 0  | Orange   | General-Purpose Input/Output 1 (GPIO 0) pin.                          |  |

| 8          | UART RX | Blue     | Universal Asynchronous Receiver-Transmitter (UART) receive data pin.  |  |

| 9          | UART TX | White    | Universal Asynchronous Receiver-Transmitter (UART) transmit data pin. |  |

| 10         | GND     | Grey     | Pin used for the ground connection.                                   |  |

# **GENERAL INPUT/OUTPUT PORT CHARACTERISTICS**

| SYMBOL              | PARAMETER                                                                                 | CONDITION                                                                                                            | Min                                       | Түре                         | Max                          | Unit |  |

|---------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------|------------------------------|------|--|

| VIL                 | FT, FTf, TTa, and NRST I/O input low                                                      | 1.7 V ≤ V <sub>DD</sub> ≤ 3.6 V                                                                                      | -                                         | -                            | 0.35V <sub>DD</sub> - 0.04   | V    |  |

|                     | level voltage                                                                             |                                                                                                                      |                                           |                              | 0.3V <sub>DD</sub> (2)       |      |  |

|                     |                                                                                           | $1.75 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V},$                                                                | _                                         | - 0.1V <sub>DD</sub> + 0.1 ( |                              |      |  |

|                     | BOOT0 I/O input low level voltage                                                         | - 40°C ≤ T <sub>A</sub> ≤105°C                                                                                       |                                           |                              | 0.1V <sub>DD</sub> + 0.1 (1) |      |  |

|                     | ,                                                                                         | $1.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V},$<br>$0^{\circ}\text{C} \le \text{T}_{A} \le 105^{\circ}\text{C}$ | -                                         | -                            | -                            |      |  |

|                     | FT, FTf, TTa, and NRST I/O input                                                          | $1.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}$                                                                  | 0.45 V <sub>DD</sub> + 0.3 <sup>(1)</sup> | _                            | -                            |      |  |

|                     | high-level voltage (4)                                                                    |                                                                                                                      | 0.7 V <sub>DD</sub> <sup>(2)</sup>        | _                            |                              |      |  |

| ViH                 |                                                                                           | $1.75 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V},$                                                                | 0.17 V <sub>DD</sub> + 0.7 <sup>(1)</sup> | -                            |                              | V    |  |

| VIII                | BOOT0 I/O input high-level voltage                                                        | - 40°C ≤ T <sub>A</sub> ≤ 105°C                                                                                      |                                           |                              | -                            | V    |  |

|                     | BOOTO I/O Input mign-level voltage                                                        | $1.7 \text{ V} \leq \text{V}_{DD} \leq 3.6 \text{ V},$                                                               |                                           |                              |                              |      |  |

|                     |                                                                                           | 0°C ≤ T <sub>A</sub> ≤ 105°C                                                                                         |                                           |                              |                              |      |  |

|                     | FT, FTf, TTa, and NRST I/O input hysteresis                                               | $1.7 \text{ V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V}$                                                         | -                                         | 10% V <sub>DD</sub>          | -                            |      |  |

|                     | BOOT0 I/O input hysteresis                                                                | $1.75 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V},$                                                                |                                           | 100 m                        |                              | V    |  |

| V <sub>HYS</sub>    |                                                                                           | - 40°C ≤ T <sub>A</sub> ≤ 105°C                                                                                      | _                                         |                              | _                            |      |  |

|                     |                                                                                           | $1.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V},$                                                                 | _                                         |                              | _                            |      |  |

|                     |                                                                                           | 0°C ≤ T <sub>A</sub> ≤ 105°C                                                                                         |                                           |                              | -                            |      |  |

| I <sub>lkg</sub>    | I/O input leakage current (3)                                                             | $V_{SS} \le V_{IN} \le V_{DD}$                                                                                       | -                                         | -                            | ±1                           | μA   |  |

| ling                | I/O FT input leakage current (4)                                                          | V <sub>IN</sub> = 5 V                                                                                                | -                                         | -                            | 3                            | μ, τ |  |

| D                   | Weak pull-up equivalent resistor (5) All pins except for PA10/PB12 (OTG_FS_ID, OTG_HS_ID) | W -W                                                                                                                 | 30                                        | 40                           | 50                           | 1.0  |  |

| R <sub>PU</sub>     | Weak pull-up equivalent resistor <sup>(5)</sup> Pins PA10/PB12 (OTG_FS_ID, OTG_HS_ID)     | $V_{IN} = V_{SS}$                                                                                                    | 7                                         | 10                           | 14                           | kΩ   |  |

|                     | Weak pull- down equivalent resistor                                                       |                                                                                                                      | 30                                        | 40                           | 50                           | kΩ   |  |

| R <sub>PD</sub>     | All pins except for PA10/PB12<br>(OTG_FS_ID, OTG_HS_ID)                                   | V <sub>IN</sub> = V <sub>DD</sub>                                                                                    |                                           |                              |                              |      |  |

|                     | Weak pull- down equivalent resistor                                                       |                                                                                                                      | 7                                         | 10                           | 14                           |      |  |

|                     | Pins PA10/PB12 (OTG_FS_ID,<br>OTG_HS_ID)                                                  |                                                                                                                      |                                           |                              |                              |      |  |

| C <sub>IO</sub> (7) | I/O pin capacitance                                                                       |                                                                                                                      | -                                         | 5                            | -                            | pF   |  |

#### Footnotes:

- 1. Guaranteed by design.

- 2. Tested in production.

- 3. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins.

- 4. To sustain a voltage higher than V<sub>DD</sub> + 0.3 V, the internal pull-up/pull-down resistors must be disabled. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins.

- 5. Pull-up resistors are designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimum (~10% order).

- 6. Pull-down resistors are designed with a true resistance in series with a switchable NMOS. This NMOS contribution to the series resistance is minimum (~10% order).

- 7. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed based on test during characterization.

# **OUTPUT VOLTAGE CHARACTERISTICS**

| SYMBOL              | PARAMETER                                | CONDITION                                                          | Min                                  | Max     | Unit                                  |

|---------------------|------------------------------------------|--------------------------------------------------------------------|--------------------------------------|---------|---------------------------------------|

| V <sub>OL</sub> (1) | Output low-level voltage for an I/O pin  | CMOS port (2)<br>I <sub>IO</sub> = 8 mA                            | -                                    | 0.4     | V                                     |

| V <sub>OH</sub> (3) | Output high-level voltage for an I/O pin | 100 - 0  MA<br>$2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}$ | VDD - 0.4                            | -       | V                                     |

| V <sub>OL</sub> (1) | Output low-level voltage for an I/O pin  | TTL port <sup>(2)</sup>                                            | -                                    | 0.4     | V                                     |

| V <sub>OH</sub> (3) | Output high-level voltage for an I/O pin | 110 = 8  mA<br>$2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}$ | 2.4                                  | -       | V                                     |

| V <sub>OL</sub> (1) | Output low-level voltage for an I/O pin  | I <sub>IO</sub> = 20 mA                                            | -                                    | 1.3 (4) | V                                     |

| V <sub>OH</sub> (3) | Output high-level voltage for an I/O pin | $2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}$                | V <sub>DD</sub> - 0.4 <sup>(4)</sup> | -       | V                                     |

| V <sub>OL</sub> (1) | Output low-level voltage for an I/O pin  | I <sub>IO</sub> = 6 mA                                             | -                                    | 0.4 (4) | V                                     |

| V <sub>OH</sub> (3) | Output high-level voltage for an I/O pin | $1.8~\text{V} \leq \text{V}_{\text{DD}} \leq 3.6~\text{V}$         | V <sub>DD</sub> - 0.4 <sup>(4)</sup> | -       | ) V                                   |

| V <sub>OL</sub> (1) | Output low-level voltage for an I/O pin  | I <sub>IO</sub> = 4 mA                                             | -                                    | 0.4 (5) | V                                     |

| V <sub>OH</sub> (3) | Output high-level voltage for an I/O pin | $1.7 \text{ V} \leq \text{V}_{DD} \leq 3.6 \text{V}$               | V <sub>DD</sub> - 0.4 <sup>(5)</sup> | -       | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

- 2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

- 3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

- 4. Based on characterization data.

- 5. Guaranteed by design.

#### **FCC 15b devices (15.105)**

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation.

If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- -Reorient or relocate the receiving antenna.

- -Increase the separation between the equipment and receiver.

- -Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- -Consult the dealer or an experienced radio/TV technician for help.

#### **FCC Part 15.21**

Information for user

You are cautioned that changes or modifications not expressly approved by the party responsible for compliance could void your authority to operate the equipment.

#### **FCC Part 15.19**

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference and (2) this device must accept any interference received, including interference that may cause undesired operation