Datasheet

# **MAMWLEXX**

Low Power Radio Module with Arm M4 Core

Move S.r.l Piazza Cavour 7 - <u>Milano 20121</u> info@move-x.it www.move-x.it

#### **TABLE OF CONTENTS**

| TABLE OF CONTENTS                                                                                                                                                                             | 1                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| REVISION HISTORY                                                                                                                                                                              | 2                                            |

| FEATURES                                                                                                                                                                                      | 3                                            |

| GENERAL DESCRIPTION                                                                                                                                                                           | 4                                            |

| ORDERING INFORMATIONS                                                                                                                                                                         | 5                                            |

| BLOCK DIAGRAM                                                                                                                                                                                 | 5                                            |

| Main System Peripherals and GPIOs Pinout: USART1/USART2 Pinout: USART1/USART2 Pinout: I2C1/I2C2/I2C3 Ports Description Peripherals                                                            | 6<br>7<br>8<br>9<br>10                       |

| MAX RATING AND EXTERNAL CHARACTERISTICS  Operating Characteristics  Absolute Characteristics  RF Characteristics  Radio                                                                       | 18<br>18<br>19<br>19<br>20                   |

| HOW TO PROGRAM & DEBUG THE MAMWLEXX  How to Develop with MAMWLEXX  Program and Debug  Use of ST-link Connector                                                                                | <b>21</b><br>21<br>21<br>22                  |

| REFERENCE SCHEMATIC                                                                                                                                                                           | 23                                           |

| LAYOUT GUIDELINES                                                                                                                                                                             | 24                                           |

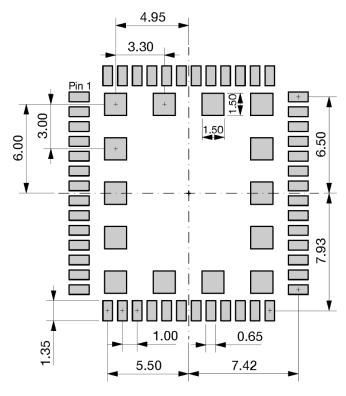

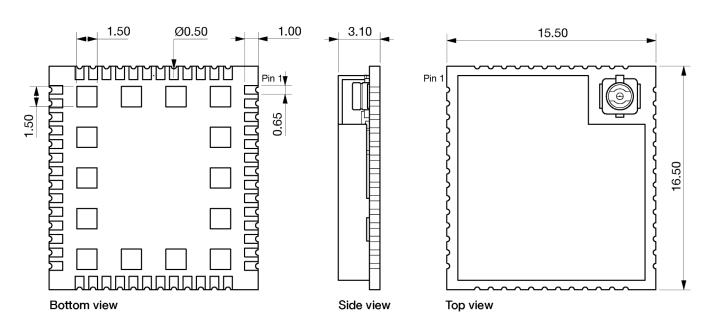

| FOOTPRINT AND DIMENSIONS  Recommended Footprint  Size and Dimensions                                                                                                                          | <b>25</b><br>25<br>25                        |

| REGULATORY INFORMATION  Regulatory Certifications  Certified Antennas  Integration Requirements  FCC Regulatory (USA)  ISED Regulatory (Canada)  EU Regulatory (Europe)  UKCA Regulatory (UK) | 26<br>26<br>26<br>26<br>27<br>28<br>29<br>30 |

#### **REVISION HISTORY**

| Revision | Date       | Notes                                                                                                                                   | Contributors   | Approver       |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|

| 1.0      | 08/03/2021 | Initial version                                                                                                                         | Marco Galli    | Gabriele Corsi |

| 1.1      | 25/01/2022 | Added Ordering Informations, Table of<br>Contents and Regulatory infos; revised<br>Operating Characteristics; updated<br>logos and URLs | Gabriele Corsi | Gabriele Corsi |

## **MAMWLEXX**

### Low Power Radio Module with Arm M4 Core

#### **FEATURES**

**CORE:** STM32WLE5Jx

Multiprotocol LPWAN 32bit Arm®Cortex® M4 MCUs, LoRa®, (G)FSK, (G)MSK, BPSK

128KB-256KB Flash, 48KB-64KB SRAM

Rich peripherals: ADC, DAC, DMA, Comparators, Timers, independent watchdog

Ultra-low power features

INTERFACES: 2xSPI, 3xI2C, 2xU(S)ART, 1xLPUART, 1xJTAG, 1xSWDIO, 1xI2S

**SIZE:** 16.5mm X 15.5mm X 2mm

CLOCK: 32MHz TCXO, 32.768KHz XTAL

**TX POWER:** low power path (up to +14 dBm), high power path (up to +22 dBm).

**RF OUTPUT:** Two variants:

50 Ohm u.FL connector

50 Ohm pin

#### **GENERAL DESCRIPTION**

MAMWLExx is a new low power radio module with a high-performance processing unit for the most complex task and high demanding applications.

The module comes with a great size of RAM and FLASH Memory which can be used for important computing calculations and to embed the biggest software applications. It even comes with a 64-bit unique identifier (DevEUI) in it, necessary to be compliant with LoRaWAN standard. Since the module is based on STM SoC, it can be programmed using ST environment itself, like STM32 Cubelde and STMCubeMX.

MAMWLExx module is designed to be easily integrated into any PCB offering two assembly variants. One with a U.FL coaxial connector on the top of the package that can be directly plugged into the antenna through a pigtail, saving space on the mainboard. The other variant, that outputs the RF signal on a 50 Ohm pin, fits you if you wish to create your own antenna design.

The module uses a high-performance ARM Cortex M4 32 bit core operating at 48 Mhz. The MAMWLExx has different types of low-power operation states, perfect for different applications, especially the ones that need power saving.

MAMWLExx implements multiple radio modulations: LoRa, (G)FSK, (G)MSK, and BPSK with different options (Bandwidth, SF, Powers, CR) to meet different needs of communication. The module includes a 32MHz TCXO to drive the RF subsystem, and it is capable of output up to +22dbm. MAMWLExx comes with a rich pinout to meet different needs. Pinout is designed to use different peripherals at the same time using different protocols like I2C, SPI, LPUART, USART. The module has 12 multiplexed pins for a 12 bit (up to 16 bits) SAR ADC with DMA support, 12 bits DAC, 2 ultra-low-power comparator, multiple timers, and independent watchdog, JTAG and SWDIO debug capabilities. MAMWLExx has up to 32 I/O, most of them 5V-tolerant. The module implements a hardware encryption/decryption accelerator for different types of standards as AES (both 128 - 256 bits) and PKA for RSA, Diffie-Hellmann, or ECC (Elliptic Curve Cryptography) over GF(p) (Galois fields).

#### **Applications:**

- Smart meters

- Supply chain

- Building automation

- Agricultural automation

- Drone Control

- GPS RTK

- Smart cities

- Retail Store sensors

- Assets Tracking

- Street Lights

- Parking Sensors

- Environmental Sensors

- Healthcare Sensors

- Remote control applications

#### **ORDERING INFORMATIONS**

| Part Number | RF Output  | Memory Size             |

|-------------|------------|-------------------------|

| MAMWLE-00   | u.Fl       | 48-KB RAM, 128-KB FLASH |

| MAMWLE-01   | 50 Ohm pin | 48-KB RAM, 128-KB FLASH |

| MAMWLE-02   | u.Fl       | 64-KB RAM, 256-KB FLASH |

| MAMWLE-03   | 50 Ohm pin | 64-KB RAM, 256-KB FLASH |

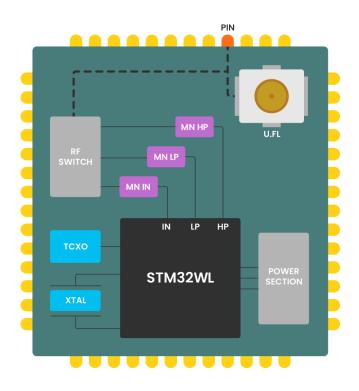

#### **BLOCK DIAGRAM**

| MN HP | Matching Network High Power Tx Path |

|-------|-------------------------------------|

| MN LP | Matching Network Low Power Tx path  |

| MN IN | Matching Network Rx path            |

MAMWLExx module embeds the following components:

- STM32WLE5Jx microcontroller, which integrates an ARM Cortex M4 processor and an SX126x LoRa transceiver on the same chip.

- 32Mhz TCXO (Temperature Compensated Crystal Oscillator) which works as the reference clock for the radio.

- 32,768KHz Oscillator which works as the Real Time Clock time reference.

- Inductor and capacitor for the internal high-efficiency SMPS step-down converter.

- RF and DC switch to select radio transmit and receive modes.

- RF matching network.

- Decoupling capacitors.

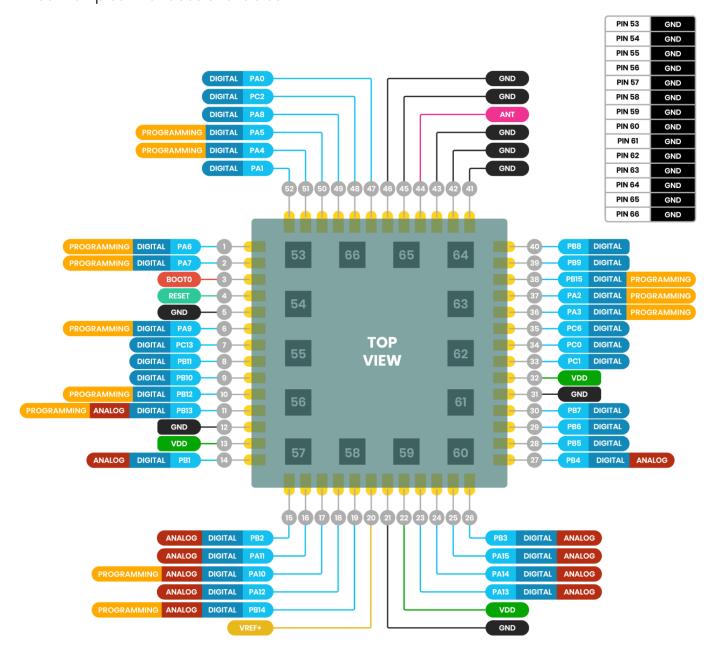

#### **PINOUT**

#### **Main System Peripherals and GPIOs**

The size of MAMWLExx is about 16,5mm X 15,5mm LGA and comes with 66 pinouts to bring all the functionality and rich peripherals of the STM32WLE5Jx microcontroller. It has multiples interfaces availables:

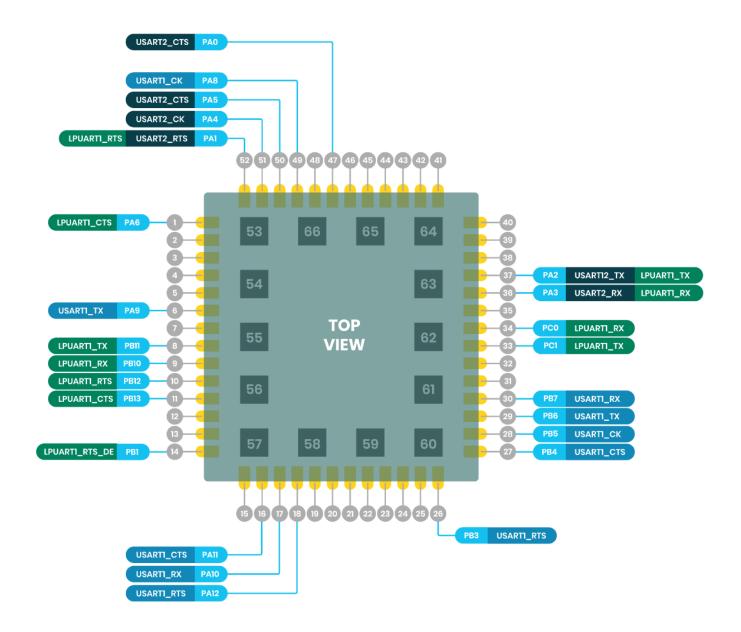

#### Pinout: USART1/USART2

#### **Pinout: USART1/USART2**

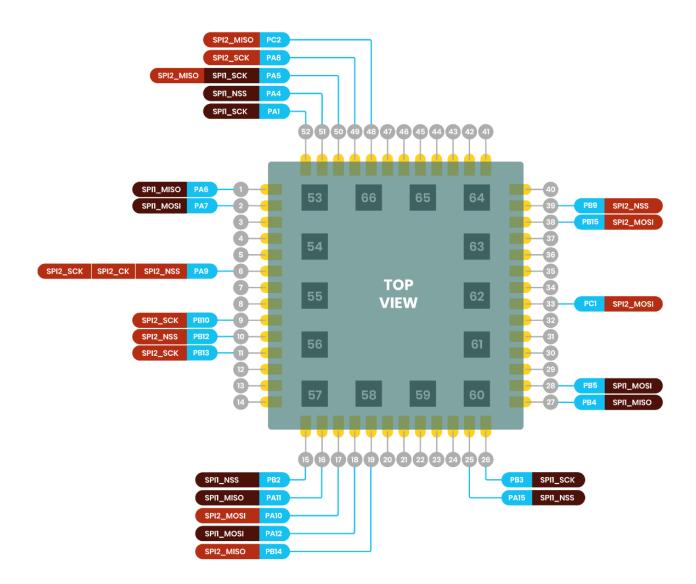

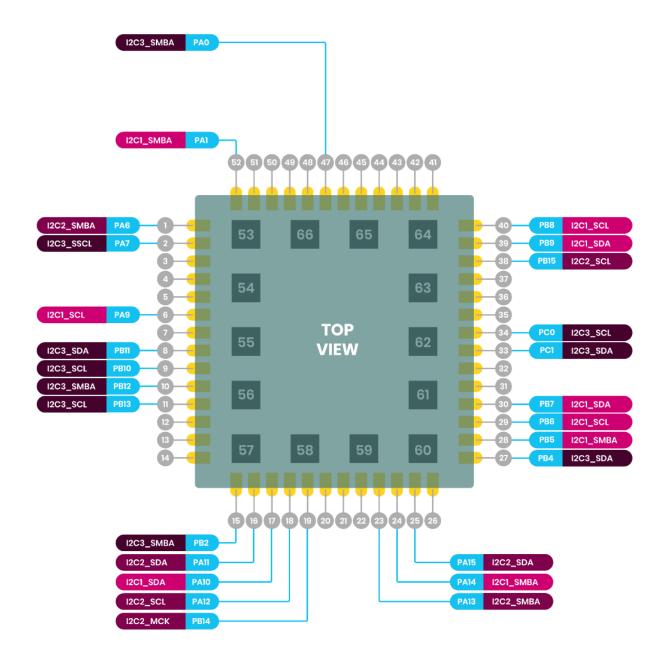

#### Pinout: I2C1/I2C2/I2C3

### **Ports Description**

|        |      | AF0      | AF1                  | AF2            | AF3                       | AF4                | AF5                   | AF6 | AF7                   |

|--------|------|----------|----------------------|----------------|---------------------------|--------------------|-----------------------|-----|-----------------------|

| Po     | ort  | SYS_AF   | TIM1/TIM2<br>/LPTIM1 | TIM1/<br>TIM2  | SPI2S2<br>TIM1/L<br>PTIM3 | 12C1/12C<br>2/12C3 | SPI1/SPI2S<br>2       | -   | USARTI<br>/USART<br>2 |

|        | PA0  | -        | TIM2_CH1             | -              | -                         | I2C3_<br>SMBA      | I2S_CKIN              | -   | USART2<br>_CTS        |

|        | PA1  | -        | TIM2_CH2             | -              | LPTIM3<br>_OUT            | I2C1_<br>SMBA      | SPI1_SCK              | -   | USART2<br>_RTS        |

|        | PA2  | LSCO     | TIM2_CH3             | -              | -                         | -                  | -                     | -   | USART2<br>_TX         |

|        | PA3  | -        | TIM2_CH4             | -              | -                         | -                  | I2S2_MCK              | -   | USART2<br>_RX         |

|        | PA4  | RTC_OUT2 | LPTIM1_<br>OUT       | -              | -                         | -                  | SPI1_NSS              | -   | USART2<br>_CK         |

|        | PA5  | -        | TIM2_CH1             | TIM2_<br>ETR   | SPI2_<br>MISO             | -                  | SPI1_SCK              | -   | -                     |

| Port A | PA6  | -        | TIM1_BKIN            | -              | -                         | I2C2_SM<br>BA      | SPI1_MISO             | -   | -                     |

|        | PA7  | -        | TIM1_CHN             | -              | -                         | I2C3_SCL           | SPI1_MOSI             | -   | -                     |

|        | PA8  | МСО      | TIM1_CH1             | -              | -                         | -                  | SPI2_SCK/<br>I2S2_Ck  | -   | USART1<br>_CK         |

|        | PA9  | -        | TIM1_CH2             | -              | SPI2_N<br>SS/I2S2<br>_WS  | I2C1_SCL           | SPI2_SCK/<br>I2S2_Ck  | -   | USART1<br>_TX         |

|        | PA10 | TIM1_CH3 | TIM1_CH3             | -              | -                         | I2C1_SDA           | SPI2_MOSI/<br>I2S2_SD | -   | USART1<br>_RX-        |

|        | PA11 | TIM1_CH4 | TIM1_CH4             | TIM1_<br>BKIN2 | LPTIM3<br>_ETR            | I2C2_SDA           | SPI1_MISO             | -   | USART1<br>_CTS        |

|        |      | AF8             | AF9 | AF10 | AF11 | AF12                 | AF13 | AF14                            | AF15             |

|--------|------|-----------------|-----|------|------|----------------------|------|---------------------------------|------------------|

| Po     | ort  | LPUART1         | -   | -    | -    | COMP1/CO<br>MP2/TIM1 | -    | TIM2/TIM16<br>/TIM17/LPTI<br>M2 | EVENOUT          |

|        | PA0  | -               | -   | -    | -    | COMP1_OUT            | -    | TIM2_ETR                        | CM4_EVENT<br>OUT |

|        | PA1  | LPUART1<br>_RTS | -   | -    | -    | -                    | -    | -                               | CM4_EVENT<br>OUT |

|        | PA2  | LPUART1<br>_TX  | -   | -    | -    | COMP2_OUT            | -    | -                               | CM4_EVENT<br>OUT |

|        | PA3  | LPUART1<br>_RX  | -   | -    | -    | -                    | -    | -                               | CM4_EVENT<br>OUT |

|        | PA4  | -               | -   | -    | -    | -                    | -    | LPTIM2_OUT                      | CM4_EVENT<br>OUT |

| Dovt A | PA5  | -               | -   | -    | -    | -                    | -    | LPTIM2_ETR                      | CM4_EVENT<br>OUT |

| Port A | PA6  | LPUART1<br>_CTS | -   | -    | -    | TIM1_BKIN            | -    | TIM16_CH1                       | CM4_EVENT<br>OUT |

|        | PA7  | -               | -   | -    | -    | COMP2_OUT            | -    | TIM17_CH1                       | CM4_EVENT<br>OUT |

|        | PA8  | -               | -   | -    | -    | -                    | -    | LPTIM2_OUT                      | CM4_EVENT<br>OUT |

|        | PA9  | -               | -   | -    | -    | -                    | -    | -                               | CM4_EVENT<br>OUT |

|        | PA10 | -               | -   | -    | -    | -                    | -    | TIM17_BKIN                      | CM4_EVENT<br>OUT |

|        | PA11 | -               | -   | -    | -    | TIM1_BKIN2           | -    | -                               | CM4_EVENT<br>OUT |

|                 |      | AF0                   | AF1                  | AF2           | AF3                           | AF4                    | AF5                 | AF6 | AF7                   |  |  |  |

|-----------------|------|-----------------------|----------------------|---------------|-------------------------------|------------------------|---------------------|-----|-----------------------|--|--|--|

| Ро              | rt   | SYS_AF                | TIM1/TIM2/L<br>PTIM1 | TIM1/<br>TIM2 | SPI2S<br>2<br>TIM1/L<br>PTIM3 | 12C1/<br>12C2/<br>12C3 | SPI1/<br>SPI2S<br>2 | -   | USARTI<br>/USART<br>2 |  |  |  |

|                 | PA12 | -                     | -                    | -             | -                             | -                      | -                   | -   | USART1_<br>RST        |  |  |  |

| Port A          | PA13 | JTMS-<br>SWDIO        | -                    | -             | -                             | I2C2_SMBA              | -                   | -   | -                     |  |  |  |

| (contin<br>ued) | PA14 | JTCK-<br>SWCLK        | LPTIM1_OUT           | -             | -                             | I2C1_SMBA              | -                   | -   | -                     |  |  |  |

|                 | PA15 | JTDI                  | TIM2_CH1             | TIM2_<br>ETR  | -                             | I2C1_SDA               | SPI1_<br>NSS        | -   | -                     |  |  |  |

|                 | PB0  | VDD_TCXO <sup>1</sup> |                      |               |                               |                        |                     |     |                       |  |  |  |

|                 | PB1  | -                     | -                    | -             | -                             | -                      | -                   | -   | -                     |  |  |  |

|                 | PB2  | -                     | LPTIM1_<br>OUT       | -             | -                             | I2C3_<br>SMBA          | SPI1_<br>NSS        | -   | -                     |  |  |  |

|                 | PB3  | JTDO-<br>TRACE<br>SWO | TIM2_<br>CH2         | -             | -                             | -                      | SPI1_<br>SCK        | 1   | USART1<br>_RTS        |  |  |  |

|                 | PB4  | NJTRST                | -                    | -             | -                             | I2C3_<br>SDA           | SPI1_<br>MISO       | -   | USART1<br>_CTS        |  |  |  |

| Port B          | PB5  | -                     | LPTIM1_IN1           | -             | -                             | I2C1_<br>SMBA          | SPI1_<br>MOSI       | 1   | USART1<br>_CK         |  |  |  |

|                 | PB6  | -                     | TIM1_<br>ETR         | -             | -                             | I2C1_<br>SCL           | -                   | 1   | USART1<br>_TX         |  |  |  |

|                 | PB7  | -                     | TIM1_<br>IN2         | -             | TIM1_<br>BKIN                 | I2C1_SDA               | -                   | -   | USART1<br>_RX         |  |  |  |

|                 | PB8  | -                     | TIM1_<br>CH2N        | -             | -                             | I2C1_<br>SCL           | -                   | -   | -                     |  |  |  |

|                 | PB9  | -                     | TIM2_<br>CH3N        | -             | -                             | I2C1_<br>SDA           | -                   | -   | -                     |  |  |  |

<sup>1.</sup> Internally connected. Not available as output Pin.

|                 |      | AF8                   | AF9 | AF10 | AF11 | AF12                     | AF13 | AF14                            | AF15             |  |  |  |

|-----------------|------|-----------------------|-----|------|------|--------------------------|------|---------------------------------|------------------|--|--|--|

| Ро              | Port |                       | -   | -    | -    | COMP1/<br>COMP2/<br>TIM1 | -    | TIM2/TIM16<br>/TIM17/LPTI<br>M2 | EVENOUT          |  |  |  |

|                 | PA12 | -                     | -   | -    | -    | -                        | -    | -                               | CM4_EVENT<br>OUT |  |  |  |

| Port A          | PA13 | IR_OUT                | -   | -    | -    | -                        | -    | -                               | CM4_EVENT<br>OUT |  |  |  |

| (contin<br>ued) | PA14 | -                     | -   | -    | -    | -                        | -    | -                               | CM4_EVENT<br>OUT |  |  |  |

|                 | PA15 | -                     | -   | -    | -    | -                        | -    | -                               | CM4_EVENT<br>OUT |  |  |  |

|                 | PB0  | VDD_TCXO <sup>1</sup> |     |      |      |                          |      |                                 |                  |  |  |  |

|                 | PB1  | LPUART1<br>RTS_DE     | -   | -    | -    | -                        | -    | LPTIM2_IN1                      | CM4_EVENT<br>OUT |  |  |  |

|                 | PB2  | -                     | -   | -    | -    | -                        | -    | -                               | CM4_EVENT<br>OUT |  |  |  |

|                 | PB3  | -                     | -   | -    | -    | -                        | -    | -                               | CM4_EVENT<br>OUT |  |  |  |

|                 | PB4  | -                     | -   | -    | -    | -                        | -    | TIM17_BKIN                      | CM4_EVENT<br>OUT |  |  |  |

| Port B          | PB5  | -                     | -   | -    | -    | -                        | -    | TIM16_BKIN                      | CM4_EVENT<br>OUT |  |  |  |

|                 | PB6  | -                     | -   | -    | -    | -                        | -    | TIM16_CH1N                      | CM4_EVENT<br>OUT |  |  |  |

|                 | PB7  | -                     | -   | -    | -    | -                        | -    | TIM17_CH1N                      | CM4_EVENT<br>OUT |  |  |  |

|                 | PB8  | -                     | -   | -    | -    | -                        | -    | TIM16_CH1                       | CM4_EVENT<br>OUT |  |  |  |

|                 | PB9  | IR_OUT                | -   | -    | -    | -                        | -    | TIM17_CH1                       | CM4_EVENT<br>OUT |  |  |  |

1. Internally connected. Not available as output Pin.

|                 |      |        | AF1                  | AF2           | AF3                        | AF4                | AF5                  | AF6 | AF7               |

|-----------------|------|--------|----------------------|---------------|----------------------------|--------------------|----------------------|-----|-------------------|

| Port            |      | SYS_AF | TIM1/TIM2<br>/LPTIM1 | TIM1/<br>TIM2 | SPI2S2/<br>TIM1/<br>LPTIM3 | 12C1/12C2<br>/12C3 | SPI1/<br>SPI2S2      | -   | USART1/<br>USART2 |

|                 | PB10 | -      | TIM2_CH3             | -             | -                          | I2C1_SCL           | -                    | -   | -                 |

| Port B          | PB11 | -      | TIM2_CH4             | -             | -                          | I2C3_SDA           | -                    | -   | -                 |

| (contin<br>ued) | PA12 | -      | TIM1_BKIN            | -             | TIM1_<br>BKIN              | I2C1_SMBA          | SPI2_NSS/<br>I2S2_WS | -   | -                 |

|                 | PA13 | -      | TIM2_CH1N            | -             | -                          | I2C1_SCL           | SPI2_SCK/<br>I2S2_CK | -   | -                 |

| Port                      |      | AF8             | AF9 | AF10 | AF11 | AF12                 | AF13 | AF14                                | AF15             |

|---------------------------|------|-----------------|-----|------|------|----------------------|------|-------------------------------------|------------------|

|                           |      | LPUART1         | -   |      |      | COMP1/<br>COMP2/TIM1 | -    | TIM2/<br>TIM16/<br>TIM17/<br>LPTIM2 | EVENOUT          |

| Port B<br>(contin<br>ued) | PB10 | LPUART1_<br>RX  | -   | -    | -    | COMP1_OUT            | -    | -                                   | CM4_EVENT<br>OUT |

|                           | PB11 | LPUART1_<br>TX  | -   | -    | -    | COMP2_OUT            | -    | -                                   | CM4_EVENT<br>OUT |

|                           | PA12 | LPUART1_<br>RTS | -   | -    | -    | -                    | -    | -                                   | CM4_EVENT<br>OUT |

|                           | PA13 | LPUART1_<br>CTS | -   | -    | -    | -                    | -    | -                                   | CM4_EVENT<br>OUT |

|        |      | AF0                   | AF1                      | AF2           | AF3                                | AF4                | AF5             | AF6 | AF7               |  |  |  |

|--------|------|-----------------------|--------------------------|---------------|------------------------------------|--------------------|-----------------|-----|-------------------|--|--|--|

| Port   |      | SYS_AF                | TIM1/<br>TIM2/<br>LPTIM1 | TIM1/<br>TIM2 | SPI2S2/<br>TIM1/<br>LPTIM3         | 12C1/12C2<br>/12C3 | SPI1/SPI<br>2S2 | -   | USARTI/<br>USART2 |  |  |  |

|        | PC0  | -                     | LPTIM1_<br>IN1           | -             | -                                  | I2C3_SCL           | SPI1_<br>MOSI   | -   | -                 |  |  |  |

|        | PC1  | -                     | LPTIM1_<br>OUT           | -             | SPI2_<br>MOSI/ I2C3_SDA<br>I2S2_SD |                    | -               | -   | -                 |  |  |  |

|        | PC2  | -                     | LPTIM1_<br>IN2           | ı             | -                                  | -                  | -               | -   | -                 |  |  |  |

|        | PC3  | FECNTRL3 <sup>1</sup> |                          |               |                                    |                    |                 |     |                   |  |  |  |

| Port C | PC4  |                       |                          |               | FECN                               | NTRL1 <sup>1</sup> |                 |     |                   |  |  |  |

|        | PC5  |                       |                          |               | FECN                               | NTRL2 <sup>1</sup> |                 |     |                   |  |  |  |

|        | PC6  | -                     | -                        | -             | -                                  | 12S2_<br>MCK       | SPI1_<br>NSS    | -   | -                 |  |  |  |

|        | PC13 | RTC_OUT1<br>/RTC_TS   | -                        | -             | -                                  | -                  | SPI1_SCK        | -   | -                 |  |  |  |

|        | PH3  | -                     | -                        | -             | -                                  | -                  | -               | -   | -                 |  |  |  |

<sup>1.</sup> Internally connected. Not available as output Pin.

|        |      | AF8                   | AF9                   | AF10 | AF11 | AF12                     | AF13 | AF14                                | AF15             |  |  |  |  |

|--------|------|-----------------------|-----------------------|------|------|--------------------------|------|-------------------------------------|------------------|--|--|--|--|

| Port   |      | LPUARTI               | -                     | -    | -    | COMP1/<br>COMP2/<br>TIM1 | -    | TIM2/<br>TIM16/<br>TIM17/<br>LPTIM2 | EVENOUT          |  |  |  |  |

|        | PC0  | LPUART1_<br>RX        | -                     | -    | -    | -                        | -    | LPTIM2_<br>IN1                      | CM4_EVEN<br>TOUT |  |  |  |  |

|        | PC1  | LPUART_<br>TX         | -                     | -    | -    | -                        | -    | -                                   | CM4_EVEN<br>TOUT |  |  |  |  |

|        | PC2  | -                     | ı                     | ı    | -    | -                        | -    | ı                                   | CM4_EVEN<br>TOUT |  |  |  |  |

|        | PC3  | FECNTRL3 <sup>1</sup> |                       |      |      |                          |      |                                     |                  |  |  |  |  |

| Port C | PC4  |                       | FECNTRL1 <sup>1</sup> |      |      |                          |      |                                     |                  |  |  |  |  |

|        | PC5  |                       | FECNTRL2 <sup>1</sup> |      |      |                          |      |                                     |                  |  |  |  |  |

|        | PC6  | -                     | ı                     | ı    | -    | -                        | -    | -                                   | CM4_EVEN<br>TOUT |  |  |  |  |

|        | PC13 | -                     | ı                     | ı    | ı    | -                        | -    | ı                                   | CM4_EVEN<br>TOUT |  |  |  |  |

|        | PH3  | -                     | -                     | -    | -    | -                        | -    | -                                   | CM4_EVEN<br>TOUT |  |  |  |  |

<sup>1.</sup> Internally connected. Not available as output Pin.

#### **Peripherals**

| Interface | Quantity |

|-----------|----------|

| I2C       | 3        |

| SPI       | 2        |

| U(S)ART   | 2        |

| LPUART    | 1        |

With a number of 36 I/O that includes:

| Task        | Quantity (Pinout) |

|-------------|-------------------|

| Digital Pin | up to 36 pins     |

| ADC         | 12 pins           |

| VREF+       | 1 pin             |

| Comparators | 2 pins            |

| DAC         | 1 pin             |

GPIO can have different operations states for output and input operation as:

- 1) Output States: Push-Pull or Open drain + pull-up/down

- 2) Input States: Floating, pull-up/down, analog

Most pins are 5V tolerant.

The module also offers different system peripheral to achieve great performances such as:

| System Peripherals                         |

|--------------------------------------------|

| 2x DMA controllers                         |

| Timers and Low Power Timer                 |

| RTC with 32-bit sub-second-wakeup counter  |

| Independent watchdog, Window watchdog      |

| Hardware Encryption/Decryption accelerator |

#### MAX RATING AND EXTERNAL CHARACTERISTICS

#### **Operating Characteristics**

| Parameter                                               | Minimum | Typical | Maximum |     |

|---------------------------------------------------------|---------|---------|---------|-----|

| Temperature                                             | -40     |         | +85     | °C  |

| Supply Voltage (VDD)                                    | 3,0     | 3,3     | 3,6     | V   |

| Supply Voltage Ripple or Noise (VDD)                    | -       | -       | 10      | mV  |

| Supply Voltage (VREF+)                                  | 2,0     | -       | VDD     | V   |

| Frequency Band                                          | 868     | -       | 915     | Mhz |

| TCXO Frequency                                          | -       | 32      | -       | Mhz |

| XTAL Frequency                                          | -       | 32,768  | -       | Khz |

| XTAL Frequency Tolerance <sup>1</sup>                   | -50     | -       | +50     | ppm |

| Power consumption <sup>2-3</sup> (shutdown mode)        | -       | 31      | 150     | nA  |

| Power consumption <sup>2-3</sup> (standby mode)         | -       | 0,255   | 0,710   | uA  |

| Power consumption <sup>2-3</sup><br>(Stop 2)            | -       | 0,885   | 2,60    | uA  |

| Power consumption <sup>2-3</sup><br>(Stop 1)            | -       | 4,20    | 20      | uA  |

| Power consumption <sup>2-3</sup><br>(Stop 0)            | -       | 400     | 570     | uA  |

| Power consumption <sup>2-3</sup><br>(Sleep mode 48 Mhz) | -       | 1,70    | 2,10    | mA  |

| Power consumption <sup>2-3</sup><br>(Run mode 48 Mhz)   | -       | 5,55    | 7,40    | mA  |

<sup>1. @ +25°</sup>C

<sup>2.</sup> The effective power consumption depends on: temperature; supply voltage; clock settings.

<sup>3.</sup> Given consumptions are for VDD = 3.3V; T = +25°C.

#### **Absolute Characteristics**

| Parameter              | Minimum | Typical | Maximum |    |

|------------------------|---------|---------|---------|----|

| Temperature            | -40     | -       | +85     | °C |

| Supply Voltage (VDD)   | -0,3    | -       | 3,6     | V  |

| Supply Voltage (VREF+) | -0,3    | -       | 3,6     | V  |

#### **RF Characteristics**

| Parameter                                  | Minimum | Typical | Maximum |     |

|--------------------------------------------|---------|---------|---------|-----|

| Output RF level (Low PA)                   | -       | -       | +14     | dBm |

| Output RF level (High PA)                  | -       | -       | +22     | dBm |

| Power consumption (PA=+10dBm) <sup>1</sup> | 15      | -       | 20      | mA  |

| Power consumption (PA=+14dBm) <sup>1</sup> | -       | -       | 26      | mA  |

| Power consumption (PA=+20dBm) <sup>1</sup> | 87      | -       | 106     | mA  |

| Power consumption (PA=+22dBm) <sup>1</sup> | -       | -       | 120     | mA  |

| Sensitivity (868Mhz, BW=125Khz SF=12)      | -       | -135,4  | -       | dBm |

| Sensitivity (868Mhz, BW=125Khz SF=7)       | -       | -124,2  | -       | dBm |

| Sensitivity (868Mhz, BW=500Khz SF=12)      | -       | -129,6  | -       | dBm |

| Sensitivity (868Mhz, BW=500Khz SF=7)       | -       | -116,2  | -       | dBm |

| Sensitivity (915Mhz, BW=125Khz SF=12)      | -       | -135,6  | -       | dBm |

| Sensitivity (915Mhz, BW=125Khz SF=7)       | -       | -122,4  | -       | dBm |

| Sensitivity (915Mhz, BW=500Khz SF=12)      | -       | -127,9  | -       | dBm |

| Sensitivity (915Mhz, BW=500Khz SF=7)       | -       | -115,1  | -       | dBm |

4. VDD = 3.3 V

#### **Radio**

The Sub-Ghz Radio is a low power radio with a high quality matching filter to operate in the band of 868 Mhz and 915 Mhz. It can use different modulation techniques such as:

| Modulation | Mode    |

|------------|---------|

| LoRa       | TX/RX   |

| (G)FSK     | TX/RX   |

| (G)MSK     | TX/RX   |

| (D)BPSK    | Only TX |

The Sub-Ghz Radio is equipped with two power amplifiers, a high efficiency one up to +14dBm, and a high power one up to +22dBm. Output power can be programmed with steps of 1 dB within 32 steps. The 32MHz TCXO guarantees great stability during transmission.

LoRa modulation can operate with different bandwidths and Spreading Factors (from 5 to 12):

| 0    | 1     | 2     | 3     | 4     | 5     | 6    | 7   | 8   | 9   | Code    |

|------|-------|-------|-------|-------|-------|------|-----|-----|-----|---------|

| 7,81 | 10,42 | 15,63 | 20,83 | 31,25 | 41,67 | 62,5 | 125 | 250 | 500 | BW[KHZ] |

It can be set in multiple differents mode of operations for LoRa Packet (Explicit/Implicit Header Mode) choosing also different coding rates:

| 0   | 1   | 2   | 3   | 4   | CR Setting  |

|-----|-----|-----|-----|-----|-------------|

| 4/4 | 4/5 | 4/6 | 4/7 | 4/8 | Coding Rate |

The radio is completely programmable to achieve the best performance needs for different kinds of application.

MAMWLExx comes with two different option:

- 1) 50 Ohm u.FL connector

- 2) 50 Ohm RF pin

The u.FL connector is mounted on top of the module together with a high performance Pi Filter, so there is no need to design any RF circuit to match the antenna. To give the best flexibility to the designers, MAMWLExx implements also a 50 Ohm RF pin variant to enhance a complete custom antenna design.

#### **HOW TO PROGRAM & DEBUG THE MAMWLEXX**

#### **How to Develop with MAMWLExx**

MAMWLExx is compatible with all the software development environments that work for the STM32 microcontroller series (e.g. STM32CubeIDE, Keil uVision, IAR Embedded).

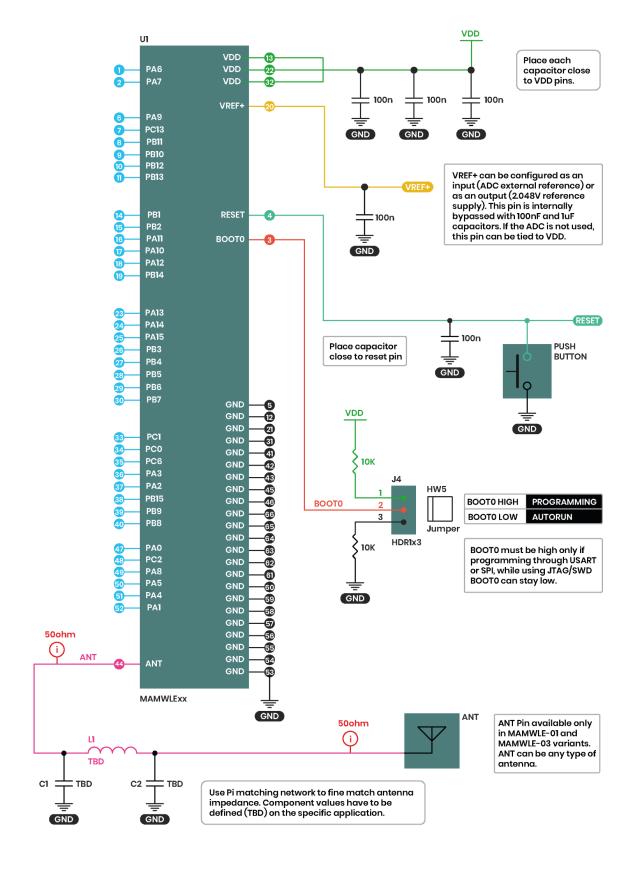

The RF switch that selects the Tx/Rx path of the module is controlled by the STM32WL by three GPIOs. Those GPIOs (PC3, PC4, PC5) aren't output in the MAMWLExx footprint, but must be driven in the firmware to use the RF part as desired (see tab). Same thing applies to pin PB0 of the STM32WL that is connected (internally) at the TCXO power supply. TCXO must be ON when using the RF part and can be switched OFF the rest of the time, reducing the overall current consumption.

This choice of the pins controlling the RF switch and the TCXO is the same as the ST NUCLEO-WL55JC development board. In this way the user can run, without any further modification, the code examples that come within the firmware packages released by ST for the STM32WL series.

Those examples in the firmware packages are also the best way to start a new project with the MAMWLExx. Another good starting point is the <u>AT Command firmware</u>, through which it is possible to use the module as a LoRa(WAN) modem, using serial commands.

| RF frontend configuration | PC4  | PC5  | PC3  | РВ0  |

|---------------------------|------|------|------|------|

| TX high output power      | Low  | High | High | High |

| TX low output power       | High | High | High | High |

| RX                        | High | Low  | High | High |

| Power-down                | Low  | Low  | Low  | Low  |

#### **Program and Debug**

There are many ways to program and debug the MAMWLExx. The MAMWLExx comes with an internal bootloader that supports boot from SPI and USART, in addition the module can also be programmed and debugged via the JTAG/SWD interface.

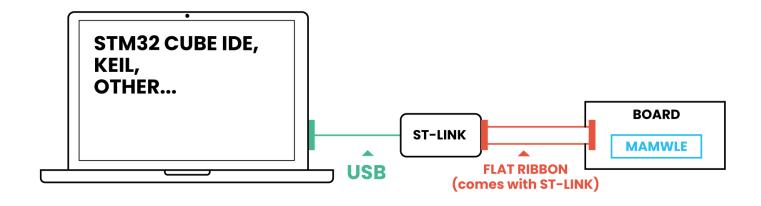

The best way to access those interfaces for programming is through the ST-LINK V3 debugger/programmer for STM32 micro series. The ST-link acts like a bridge between the board and the PC. It communicates with the PC via a microB-USB cable and has many headers for connecting with various subsets of the SPI/USART/JTAG/SWD interfaces of the module. If you would like to program the module using SPI or USART see <a href="May2606"><u>AN2606</u></a> by ST.

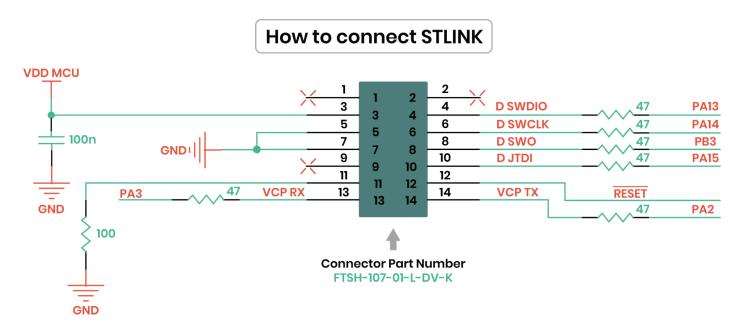

Among all the possible ST-link V3 headers, below we indicate an easy way of connection that suits either programming and debugging. For further information on other ST-link possibilities please see the <u>UM2448</u> user manual by ST.

#### **Use of ST-link Connector**

ST-Link connector supports SWD/JTAG interface for programming and debugging the application and provides a virtual comport (COM or VCP) that makes a simple printing string in a serial terminal. To be able to connect the board to the connector, the board should have a twin header connected to the module like shown in the figure. While programming through ST-Link is not necessary to connect BOOT0 to VCC.

#### REFERENCE SCHEMATIC

#### **LAYOUT GUIDELINES**

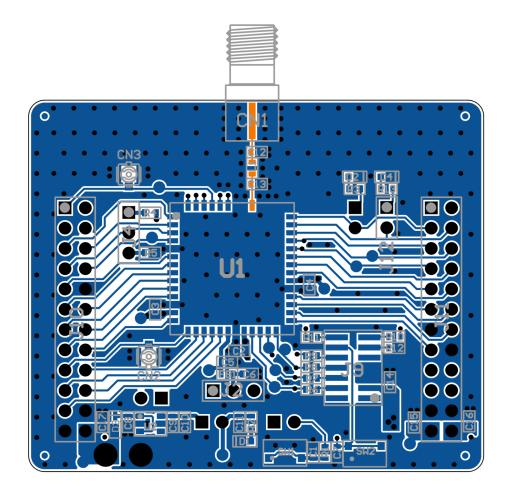

When integrating the MAMWLExx module into a custom PCB, some layout guidelines have to be followed. The DVK board project can be downloaded <a href="here">here</a> for help. This is a 4 layer board which was used for certification tests.

In general, to maintain good RF performance and avoid any side effect, pay attention to the following points:

- Use the same number of PCB layers as reference design whenever possible. If it is necessary to use a different set of layers, make sure that the distance between the top layer and the reference ground plane is the same. Always make sure to use 50 Ohm nominal impedance RF traces (this is applicable only with 50 Ohm Pin variants).

- Use as much continuous and unified ground plane floods as possible, especially on top and bottom reference layer.

- Use as many grounding vias as possible, especially near ground pads, to minimize parasitic inductance.

- Avoid any cut on ground planes, especially under RF traces. Keep all the components away from RF traces.

- Place the RF related parts far away from DC-DC converters or any switching current devices.

- Avoid routing any I/O line close or beneath the RF lines.

#### **FOOTPRINT AND DIMENSIONS**

#### **Recommended Footprint**

#### **Size and Dimensions**

All dimensions in mm.

#### **REGULATORY INFORMATION**

#### **Regulatory Certifications**

MAMWLExx module holds certifications for the following regions:

| Region        | Regulatory ID             |

|---------------|---------------------------|

| Europe (EU)   | N/A                       |

| USA (FCC)     | 2A3LJ-MAMWLE <sup>1</sup> |

| UK (UKCA)     | N/A                       |

| Canada (ISED) | 28058-MAMWLE <sup>1</sup> |

#### 1. Certification pending

#### **Certified Antennas**

MAMWLExx module was tested with the following antennas. The OEM can choose another vendor's antenna but must take care it is of the same type, and doesn't exceed the gain listed below.

| Manufacturer | Part Number | Туре     | Gain    | Impedance |

|--------------|-------------|----------|---------|-----------|

| ANT S.r.l.   | B01-000     | Monopole | 2,15dBi | 50 Ohm    |

#### **Integration Requirements**

To guarantee regulatory compliance, when integrating the MAMWLExx module into an OEM device, it is necessary to meet the following requirements, divided by regulatory agency. The manufacturer is not responsible for any radio or TV interference caused by unauthorized modifications to the equipment. Such modifications could void the user's authority to operate the equipment

#### FCC Regulatory (USA)

#### Federal Communication Commission Interference Statement

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules.

These limits are designed to provide reasonable protection against harmful interference in a residential installation.

This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation.

If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

**FCC Caution**: Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

- (1) this device may not cause harmful interference, and

- (2) this device must accept any interference received, including interference that may cause undesired operation.

#### <u>Host Product Labeling</u>

The product where the MAMWLExx module is integrated into must be labeled in a visible area with the following wording: "Contains FCC ID: 2A3LJ-MAMWLE".

#### <u>Information to the End User</u>

The OEM integrator must guarantee not to provide to the end user any information on how to install or remove RF module in the instruction manual of the end product.

The end user shall include all required regulatory information as shown in this manual.

This equipment should be installed and operated with a minimum distance of 20 cm between the device and the user or bystanders.

#### **Integration informations**

The OEM can choose a different antenna model than the one used in the module's test setup, but must take care it is of the same type, and doesn't exceed the maximum gain listed before. Refer to FCC Part 15.204(c)(4) for further information. If the OEM needs to increase antenna gain and either change antenna type, a Class II permissive change application is required.

The module is limited to installation in mobile or fixed applications. Separate approval is required for all other operating configurations, including portable configuration.

The module complies with FCC Part 15 transmitter rules, the OEM is responsible for compliance to any other FCC rules that apply to the host not covered by the modular transmitter grant of certification.

The OEM must also certify the final end product to comply with FCC Part 15B (unintentional radiators). Integration into devices that are directly or indirectly connected to AC lines must be added with Class II Permissive Change.

#### ISED Regulatory (Canada)

#### Innovation, Science and Economic Development Statement

This device complies with Industry Canada licence-exempt RSS standard(s). Operation is subject to the following two conditions:

- (1) this device may not cause interference, and

- (2) this device must accept any interference, including interference that may cause undesired operation of the device.

Le présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio exempts de licence. L'exploitation est autorisée aux deux conditions suivantes :

- (1) l'appareil ne doit pas produire de brouillage, e

- (2) l'utilisateur de l'appareil doit accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

This equipment complies with Industry Canada radiation exposure limits set forth for an uncontrolled environment.

Cet équipement est conforme à l'exposition aux rayonnements Industry Canada limites établies pour un environnement non contrôlé.

#### **Host Product Labeling**

The product where the MAMWLExx module is integrated into must be labeled in a visible area with the following wording: "Contains IC ID: 28058-MAMWLE".

#### Plaque signalétique du produit final

Le produit final doit être étiqueté dans un endroit visible avec l'inscription suivante: "Contient des IC: 28058-MAMWLE".

#### Information to the End User

The OEM integrator must guarantee not to provide to the end user any information on how to install or remove RF module in the instruction manual of the end product.

The end user shall include all required regulatory information as shown in this manual.

This equipment should be installed and operated with a minimum distance of 20 cm between the device and the user or bystanders.

#### <u>Informations à l'utilisateur final</u>

L'intégrateur OEM doit garantir de ne fournir à l'utilisateur final aucune information sur la manière d'installer ou de retirer le module RF dans le manuel d'instructions du produit final.

L'utilisateur final doit inclure toutes les informations réglementaires requises comme indiqué dans ce manuel. Cet équipement doit être installé et utilisé avec une distance minimale de 20 cm entre l'appareil et l'utilisateur ou les passants.

#### **EU Regulatory (Europe)**

MAMWLExx has been tested for compliance with relevant standards for the EU market. It is recommended to use antennas with a gain equal to or less than those used for certifications to retain compliance. The OEM should consult with a qualified test house before entering their device into an EU member country to make sure all regulatory requirements have been met for their device. Test reports are available on request.

#### **EU Statement of Compliance**

Manufacturer: **Move S.r.l.**

Piazza Cavour, 7 20121 - Milano

Italy

Product: **MAMWLE-00**

MAMWLE-01 MAMWLE-02 MAMWLE-03

Applied Standards: EN 301 489-1 V2.2.0

EN 301 489-3 V2.1.1 ETSI EN 300 220-1 V3.1.1 ETSI EN 300 220-2 V3.2.1

EN 50663:2017 IEC 62368-1:2018 EN IEC 63000:2018

#### Declaration:

The manufacturer declares that the product complies with specified above and meets the essential requirements of the Directive: **2014/53/EU** (RED), **2011/65/EU** (ROHS). This declaration of conformity is issued under the sole responsibility of the manufacturer.

Place of Issue: Lucca Date of Issue: 15/05/2021

CEO

fedinando fradioni

#### **UKCA Regulatory (UK)**

#### **EU Statement of Compliance**

Manufacturer: Move S.r.l.

Piazza Cavour, 7 20121 - Milano

Italy

Product: MAMWLE-00

MAMWLE-01 MAMWLE-02 MAMWLE-03

Applied Standards: EN 301 489-1 V2.2.0

EN 301 489-3 V2.1.1 EN 300 220-1 V3.1.1 EN 300 220-2 V3.2.1 EN 50663:2017 EN 62368-1:2018 EN 63000:2018

#### Declaration:

The manufacturer declares that the product complies with specified above and meets the essential requirements of the Legislations: Radio Equipment Regulations 2017, Restriction of the Use of Certain Hazardous Substances in Electrical and Electronic Equipment Regulations 2012. This declaration of conformity is issued under the sole responsibility of the manufacturer.

Place of Issue: Lucca Date of Issue: 02/02/2022

fedinons fraction