# User Guide

03ACCY0002

*Bluetooth v4.2 Dual-Mode USB HCI Module*

*Version 1.3*

---

## SCOPE

This document describes key hardware aspects of the Enovation Controls 03ACCY0002 module. This document is mainly intended to assist device manufacturers and related parties with the integration of this module into their host devices. Data in this document are drawn from several sources including data sheets for the Cypress CYW20704A2

## 1 OPERATIONAL DESCRIPTION

The 03ACCY0002 modules leverage the Cypress CYW20704 A2 chipset to provide exceptionally low power consumption with outstanding range for OEMs needing both Classic Bluetooth. The Bluetooth v4.2 core specification shortens your development time and provides enhanced throughput, security and privacy.

The 03ACCY0002 modules are ideal when designers need both performance and minimum size. For maximum flexibility in integration, they support a host USB interface, I<sup>2</sup>S and PCM audio interfaces, GPIO, and Cypress' GCI coexistence (2-Wire).

## 2 BLOCK DIAGRAM AND DESCRIPTIONS

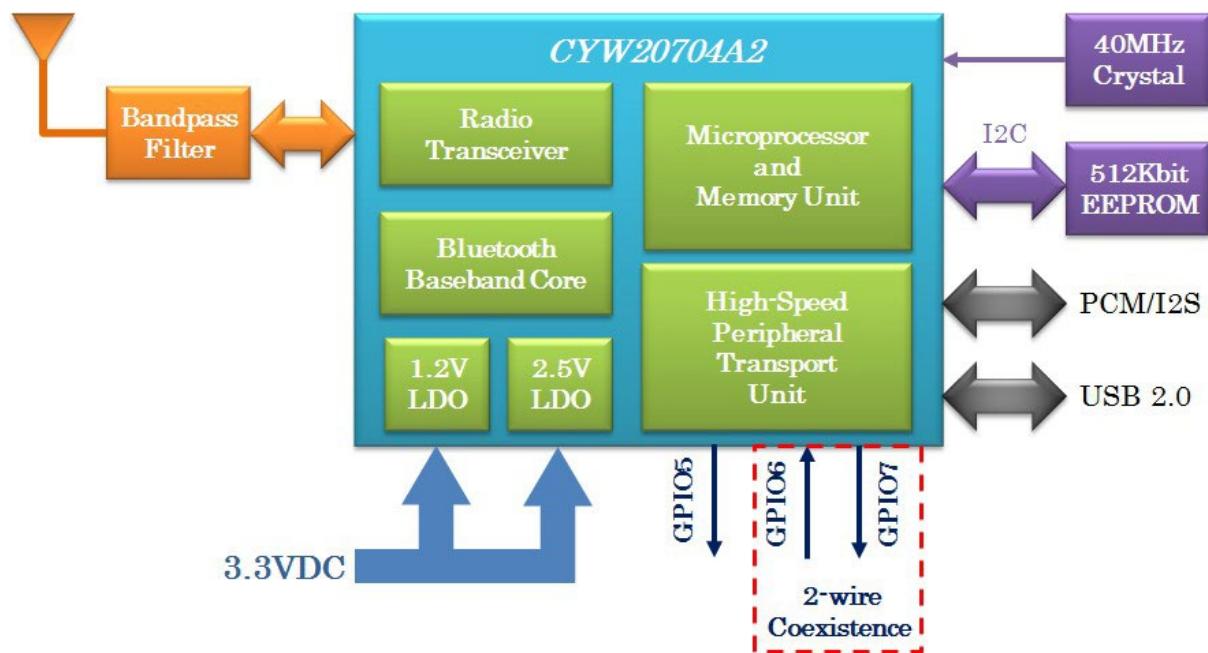

Figure 1: 03ACCY0002 module block diagram

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>CYW20704A2<br/>(Main chip)</b> | The 03ACCY0002 is based on CYW20704A2 dual mode chip. The chip is a single-chip radio with on-chip LDO regulators and baseband IC for Bluetooth 2.4 GHz systems including EDR to 3 Mbps. Dedicated signal and baseband processing is included for full Bluetooth operation. The chip provides I <sup>2</sup> S/PCM and USB interfaces. There are two general purpose I/Os be configured for proprietary of Cypress GCI used and a general purpose I/O can be configured for scan/inquire/paging/data traffic of indicator. These three I/O pins are controlled by firmware. |

| <b>Antenna</b>                    | Ceramic Monopole Chip Antenna                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <b>EEPROM</b>                     | There are 512 k bits EEPROM embedded on the 03ACCY0002 which can be used to store parameters, such as BD_ADDR, USB enumeration information, maximum TX power, PCM configuration, USB product ID, USB vendor ID, and USB product description.                                                                                                                                                                                                                                                                                                                                |

| <b>Crystal</b>                    | The embedded 40 MHz crystal is used for generating the clock for the entire module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

### 3 SPECIFICATIONS

*Table 1: 03ACCY0002 specifications*

| Categories                    | Feature                | Implementation                                    |

|-------------------------------|------------------------|---------------------------------------------------|

| <b>Wireless Specification</b> | Bluetooth®             | V4.2 Dual Mode – BR / EDR                         |

|                               | Frequency              | 2.402 - 2.480 GHz                                 |

|                               | Maximum Transmit Power | Class 1<br>+8 dBm from antenna                    |

|                               | Receive Sensitivity    | -94 dBm                                           |

|                               | Range                  | Circa 100 meters                                  |

|                               | Data Rates             | Up to 3 Mbps (over-the-air)                       |

| <b>Host Interface</b>         | USB                    | Full speed USB 2.0                                |

|                               | GPIO                   | 3.3V for all general purpose I/Os                 |

|                               | HCI                    | Host Controller Interface over USB                |

| <b>Operational Modes</b>      |                        |                                                   |

| <b>EEPROM</b>                 | 2-wire                 | 512 K bits                                        |

| <b>Coexistence</b>            | 802.11 (Wi-Fi)         | 2-Wire Cypress Global Coexistence Interface (GCI) |

| <b>Supply Voltage</b>         | Supply                 | 3.0V - 3.6V                                       |

| <b>Power Consumption</b>      | Current                | Idle Mode ~8 mA<br>File Transfer ~43 mA           |

| <b>Antenna Options</b>        |                        |                                                   |

| <b>Physical</b>               | Dimensions             | 8.5 x 12.85 x 1.9 mm                              |

| <b>Environmental</b>          | Operating              | -30° C to +85° C                                  |

|                               | Storage                | -40° C to +85° C                                  |

| <b>Miscellaneous</b>          | Lead Free              | Lead-free and RoHS-compliant                      |

| <b>Approvals</b>              |                        |                                                   |

|                               | FCC/IC                 | 03ACCY0002                                        |

## 4 PIN DEFINITIONS

Table 2: 03ACCY0002 pin definitions

| Pin No. | Pin Name        | I/O           | Supply Domain | Description                                                      | If Unused |

|---------|-----------------|---------------|---------------|------------------------------------------------------------------|-----------|

| 1       | NC              |               |               |                                                                  | NC        |

| 2       | NC              |               |               |                                                                  |           |

| 3       | GND             | GND           |               | Ground                                                           | GND       |

| 4       | USB_D+          | Bidirectional | 3V3           | USB data plus                                                    | N/A       |

| 5       | USB_D-          | Bidirectional | 3V3           | USB data negative                                                | N/A       |

| 6       | GND             | GND           |               | Ground                                                           | GND       |

| 7       | NC              |               |               |                                                                  | NC        |

| 8       | RESET           | Input         | 3v3           | Active-low reset input                                           | N/A       |

| 9       | 3v3             | Input         | 3v3           | Module main DC power supply, Input to internal 1.2V and 2.5V LDO | N/A       |

| 10      | NC              |               |               |                                                                  | NC        |

| 11      | GND             | GND           |               | Ground                                                           | GND       |

| 12      | GND             | GND           |               | Ground                                                           | GND       |

| 13      | GND             | GND           |               | Ground                                                           | GND       |

| 14      | GND             | GND           |               | Ground                                                           | GND       |

| 15      | GND             | GND           |               | Ground                                                           | GND       |

| 16      | GND             | GND           |               | Ground                                                           | GND       |

| 17      | RF              |               |               | 03ACCY0002-ST RF signal output (50Ω)<br>03ACCY0002-              |           |

| 18      | GND             | GND           |               | Ground                                                           | GND       |

| 19      | I2S_WS/PCM_SYNC | Bidirectional | 3V3           | PCM sync/I2S word select                                         | NC        |

| 20      | I2S_CLK/PCM_CLK | Bidirectional | 3V3           | PCM/I2S clock                                                    | NC        |

| 21      | I2S_DI/PCM_IN   | Bidirectional | 3V3           | PCM/I2S data input                                               | NC        |

| 22      | I2S_OUT/PCM_OUT | Bidirectional | 3V3           | PCM/I2S data output                                              | NC        |

| 23      | NC              |               |               |                                                                  | NC        |

| 24      | GND             | GND           |               | Ground                                                           | GND       |

| 25      | BT_SECI_IN      | Input         | 3V3           | Coexistence data input                                           | NC        |

| Pin No. | Pin Name    | I/O           | Supply Domain | Description                    | If Unused |

|---------|-------------|---------------|---------------|--------------------------------|-----------|

| 26      | BT_SECI_OUT | Output        | 3V3           | Coexistence data output        | NC        |

| 27      | NC          |               |               |                                | NC        |

| 28      | GPIO_5      | Bidirectional | 3V3           | Programmable input/output line | NC        |

## 5 DC ELECTRICAL CHARACTERISTICS

Table 3: Recommended operating conditions

| Rating                | Min | Max  | Unit |

|-----------------------|-----|------|------|

| Storage temperature   | -40 | +150 | °C   |

| Operating Temperature | -30 | +85  | °C   |

| 3V3 Input             | 3.0 | 3.6  | V    |

Table 4: Digital I/O characteristics

| Normal Operation                                             | Min     | Typ. | Max | Unit    |

|--------------------------------------------------------------|---------|------|-----|---------|

| $V_{IL}$ Input Low Voltage ( $VDDO = 3.3V$ )                 | -       | -    | 0.8 | V       |

| $V_{IH}$ Input High Voltage ( $VDDO = 3.3V$ )                | 2.0     | -    | -   | V       |

| $V_{OL}$ Output Low Voltage                                  | -       | -    | 0.4 | V       |

| $V_{OH}$ Output High Voltage                                 | 3V3-0.4 | -    | -   | V       |

| $I_{IL}$ Input Low Current                                   | -       | -    | 1.0 | $\mu$ A |

| $I_{IH}$ Input High Current                                  | -       | -    | 1.0 | $\mu$ A |

| $I_{OL}$ Output Low Current ( $VDDO = 3.3V, V_{OL} = 0.4V$ ) | -       | -    | 2.0 | mA      |

| $I_{OH}$ Output Low Current ( $VDDO = 3.3V, V_{OH} = 2.9V$ ) | -       | -    | 2.0 | mA      |

| $C_{IN}$ Input Capacitance                                   | -       | -    | 0.4 | pF      |

Table 5: Current consumption

| Normal Operation | Peak (8 dBm) | Unit |

|------------------|--------------|------|

| Idle             | 8            | mA   |

| Inquiry          | 23           | mA   |

| File Transfer    | 43           | mA   |

## 6 RF CHARACTERISTICS

Table 6: BDR/EDR transmitter characteristics (Input = 3V3 @ 25 °C)

| Parameter                                 | Min                       | Typ. | Max | BT. Spec. | Unit |     |

|-------------------------------------------|---------------------------|------|-----|-----------|------|-----|

| GFSK Maximum RF Transmit Power            | 6                         | 8    | 10  | 20        | dBm  |     |

| EDR Maximum RF Transmit Power             | 2                         | 4    | 6   | 20        | dBm  |     |

| RF power variation over temperature range | -                         | 2.0  | -   | -         | dB   |     |

| RF power variation over BT band           | -                         | 2    | -   | -         | dB   |     |

| RF power control step                     | 2                         | 4    | 8   | -         | dB   |     |

| Initial Carrier Frequency Tolerance       | -                         | 10   | -   | ±75       | kHz  |     |

| 20 dB Bandwidth                           | -                         | 920  | -   | 1000      | kHz  |     |

| In-Band Spurious Emissions                | 1.0 MHz <  M-N  < 1.5 MHz | -    | -   | -39       | -26  | dBc |

|                                           | 1.5 MHz <  M-N  < 2.5 MHz | -    | -   | -39       | -20  | dBm |

|                                           | M-N  ≥ 2.5 MHz            | -    | -   | -47       | -40  | dBm |

| Drift rate                                | -                         | 10   | -   | +/-25     | kHz  |     |

| ΔF1Avg                                    | -                         | 152  | -   | 140<>175  | kHz  |     |

| ΔF2Max                                    | 100                       | -    | -   | 99.9      | %    |     |

| ΔF2Avg / ΔF1Avg                           | -                         | 1.0  | -   | ≥ 0.8     |      |     |

| LE ΔF1Avg                                 | -                         | 245  | -   | 225<>275  | kHz  |     |

| LE ΔF2Max                                 | 100                       | -    | -   | 99.9      | %    |     |

| LE ΔF2Avg / ΔF1Avg                        | -                         | 1.0  | -   | ≥ 0.8     |      |     |

Table 7: BDR/EDR receiver sensitivity (Input = 3V3 @ 25 °C)

| Parameter             | Conditions                     | Min | Typ. | Max | BT. Spec. | Unit |

|-----------------------|--------------------------------|-----|------|-----|-----------|------|

| Sensitivity           | GFSK, 0.1% BER, 1Mbps          | -90 |      | -70 | -         | dBm  |

|                       | π/4-DQPSK, 0.01% BER, 2Mbps    | -94 |      | -70 | -         | dBm  |

|                       | 8-DPSK, 0.01% BER, 3Mbps       | -87 |      | -70 | -         | dBm  |

| Sensitivity variation | All Modulations (Over BT band) | 2   |      |     |           | dB   |

## 7 INTERFACE

### 7.1. Global Coexistence Interface

The 03ACCY0002 supports the proprietary Cypress Global Coexistence Interface (GCI) which is a two-wire interface.

The following key features are associated with the interface:

- Enhanced coexistence data can be exchanged over GCI\_SECI\_IN and GCI\_SECI\_OUT a two-wire interface, one serial input (GCI\_SECI\_IN), and one serial output (GCI\_SECI\_OUT). The both pins are controlled by the configuration file that is stored in EEPROM from the host.

- It supports generic UART communication between WLAN and Bluetooth devices.

- To conserve power, it is disabled when inactive.

- It supports automatic resynchronization upon waking from sleep mode.

- It supports a baud rate of up to 4 Mbps.

**Table 8: BT GCI two-wire coexistence**

| Coexistence Signal Name | Signal Assignment |

|-------------------------|-------------------|

| BT_SECI_IN              | GPIO_6            |

| BT_SECI_OUT             | GPIO_7            |

## 7.2. USB Interface

03ACCY0002 has a full-speed (12 Mbps) USB interface for communicating with other compatible digital devices. The USB interface on the 03ACCY0002 acts as a USB peripheral, responding to requests from a master host controller.

03ACCY0002 supports the Universal Serial Bus Specification (USB v2.0 Specification) and USB Battery Charging Specification, available from <http://www.usb.org>. For more information on how to integrate the USB interface on 03ACCY0002d located in the following section: [USB Dongle Design Example Using 03ACCY0002](#).

The following USB interface features are supported:

- USB Protocol, revision 2.0, full-speed compliant with LPM support (up to 12 Mbps)

- Bluetooth HCI

- Integrated detach resistor

- USB termination when interface is not in use

- Internal modules, certification, and non-specification compliant operation

## 7.3. PCM Interface

The 03ACCY0002 supports two independent PCM interfaces that share the pins with I<sup>2</sup>S interfaces. The PCM interface on the 03ACCY0002 can connect to linear PCM Codec devices in master or slave mode. In master mode, the 03ACCY0002 generates the PCM\_CLK and PCM\_SYNC signals; in slave mode, these signals are provided by another master on the PCM interface and are inputs to the 03ACCY0002.

The configuration of the PCM interface may be adjusted by the host through the use of vendor-specific HCI commands.

### 7.3.1. Slot Mapping

The 03ACCY0002 supports up to three simultaneous full-duplex SCO or eSCO channels through the PCM interface. These three channels are time-multiplexed onto the single PCM interface by using a time-slotted scheme where the 8 kHz or 16 kHz audio sample interval is divided into as many as 16 slots. The number of slots is dependent on the selected interface rate of 128 kHz, 512 kHz, or 1024 kHz. The corresponding number of slots for these interface rates is 1, 2, 4, 8, and 16, respectively. Transmit and receive PCM data from an SCO channel is always mapped to the same slot. The PCM data output driver tristates its output on unused slots to allow other devices to share the same PCM interface signals. The data output driver tristates its output after the falling edge of the PCM clock during the last bit of the slot.

### 7.3.2. Frame Synchronization

The 03ACCY0002 supports both short- and long-frame synchronization in both master and slave modes. In short-frame synchronization mode, the frame synchronization signals an active-high pulse at the audio frame rate that

is a single-bit period in width and is synchronized to the rising edge of the bit clock. The PCM slave looks for a high on the falling edge of the bit clock and expects the first bit of the first slot to start at the next rising edge of the clock.

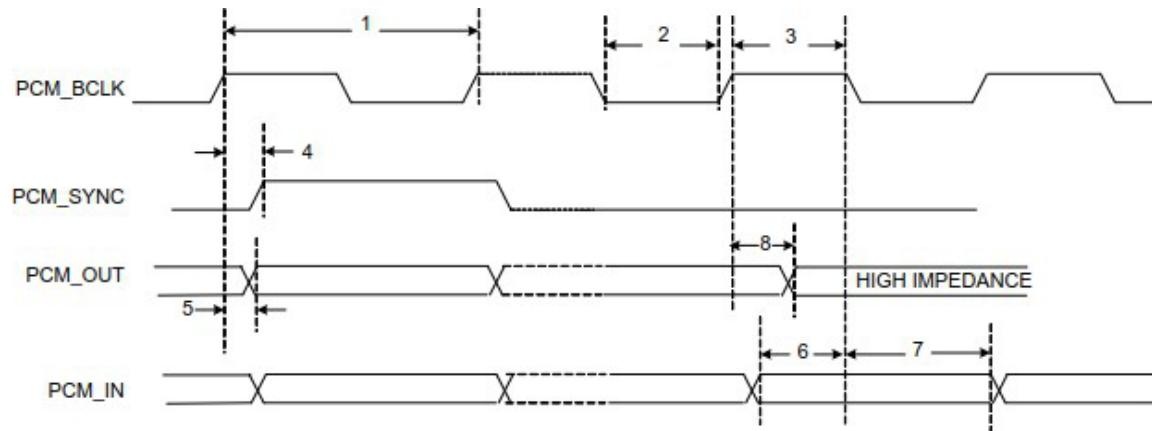

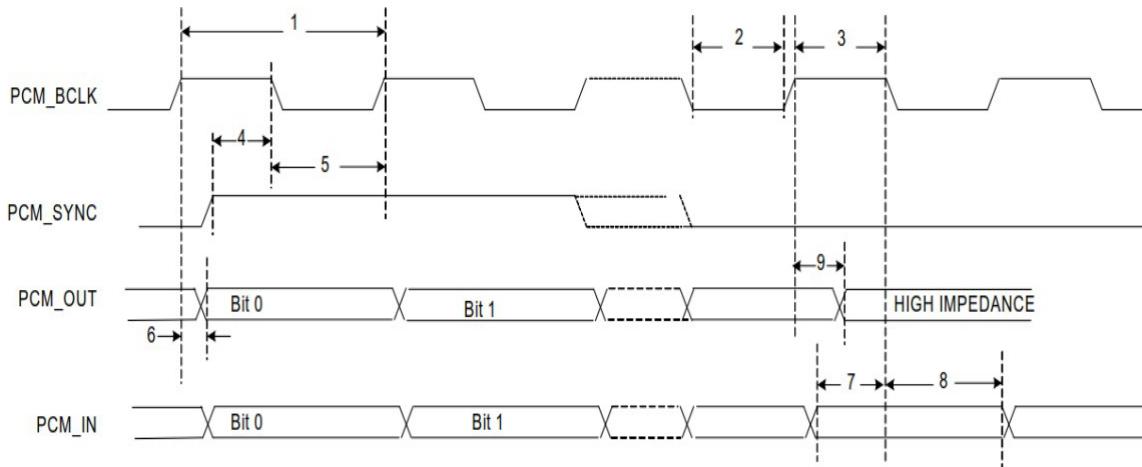

Figure 2 and Table 9 shows PCM Timing Diagram and Specifications for the master mode of short-frame.

Figure 2: PCM timing diagram (Short-Frame Sync, Master Mode)

Table 9: PCM Interface timing specifications (Short-Frame Sync, Master Mode)

| Ref No. | Characteristics                                                                              | Minimum | Typical | Maximum | Unit |

|---------|----------------------------------------------------------------------------------------------|---------|---------|---------|------|

| 1       | PCM bit clock frequency                                                                      | -       | -       | 12      | MHz  |

| 2       | PCM bit clock LOW                                                                            | 41      | -       | -       | ns   |

| 3       | PCM bit clock HIGH                                                                           | 41      | -       | -       | ns   |

| 4       | PCM_SYNC setup                                                                               | 0       | -       | 25      | ns   |

| 5       | PCM_OUT delay                                                                                | 0       | -       | 25      | ns   |

| 6       | PCM_IN setup                                                                                 | 8       | -       | -       | ns   |

| 7       | PCM_IN hold                                                                                  | 8       | -       | -       | ns   |

| 8       | Delay from rising edge of PCM_BCLK during last bit period to PCM_OUT becoming high impedance | 0       | -       | 25      | ns   |

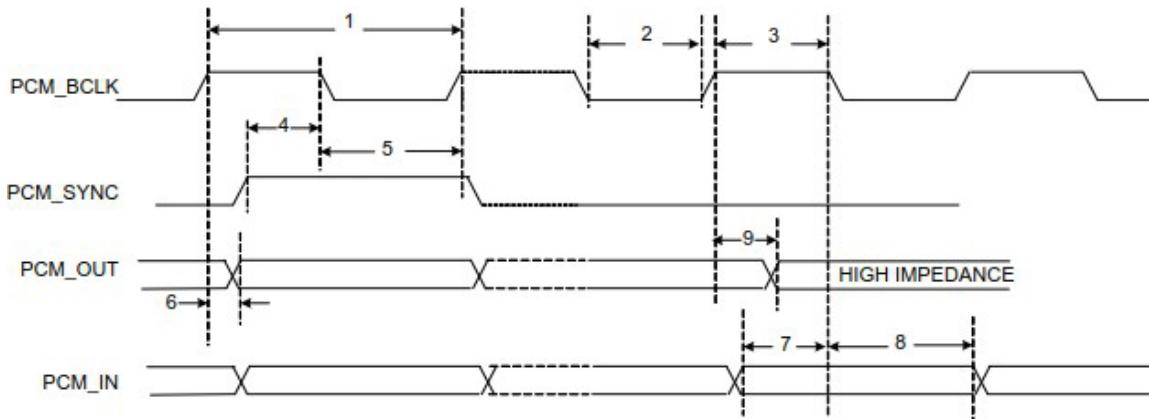

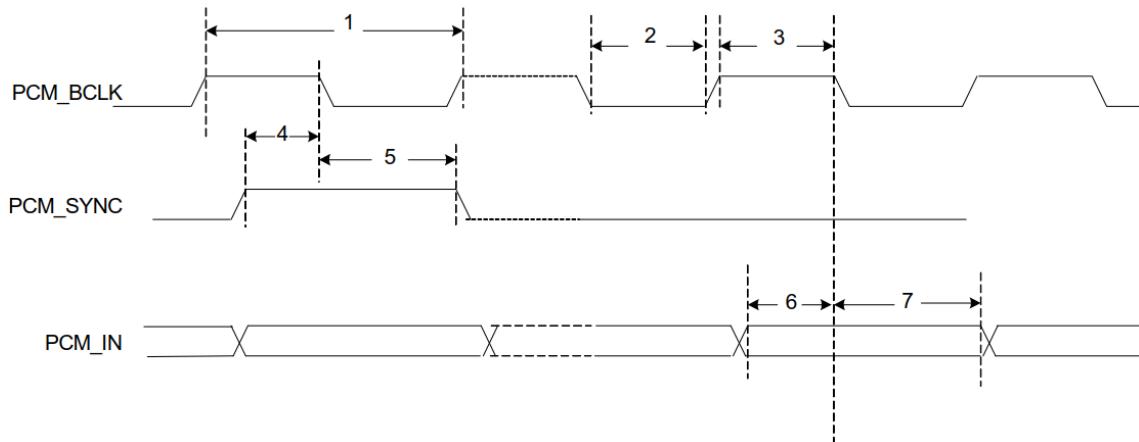

Figure 3 and Table 10 shows PCM Timing Diagram and Specifications for the slave mode of short-frame.

Figure 3: PCM timing diagram (Short-Frame Sync, Slave Mode)

Table 10: PCM Interface timing specifications (Short-Frame Sync, Slave Mode)

| Ref No. | Characteristics                                                                              | Minimum | Typical | Maximum | Unit |

|---------|----------------------------------------------------------------------------------------------|---------|---------|---------|------|

| 1       | PCM bit clock frequency                                                                      | -       | -       | 12      | MHz  |

| 2       | PCM bit clock LOW                                                                            | 41      | -       | -       | ns   |

| 3       | PCM bit clock HIGH                                                                           | 41      | -       | -       | ns   |

| 4       | PCM_SYNC setup                                                                               | 8       | -       | -       | ns   |

| 5       | PCM_SYNC_hold                                                                                | 8       | -       | -       | ns   |

| 6       | PCM_OUT delay                                                                                | 0       | -       | 25      | ns   |

| 7       | PCM_IN setup                                                                                 | 8       | -       | -       | ns   |

| 8       | PCM_IN hold                                                                                  | 8       | -       | -       | ns   |

| 9       | Delay from rising edge of PCM_BCLK during last bit period to PCM_OUT becoming high impedance | 0       | -       | 25      | ns   |

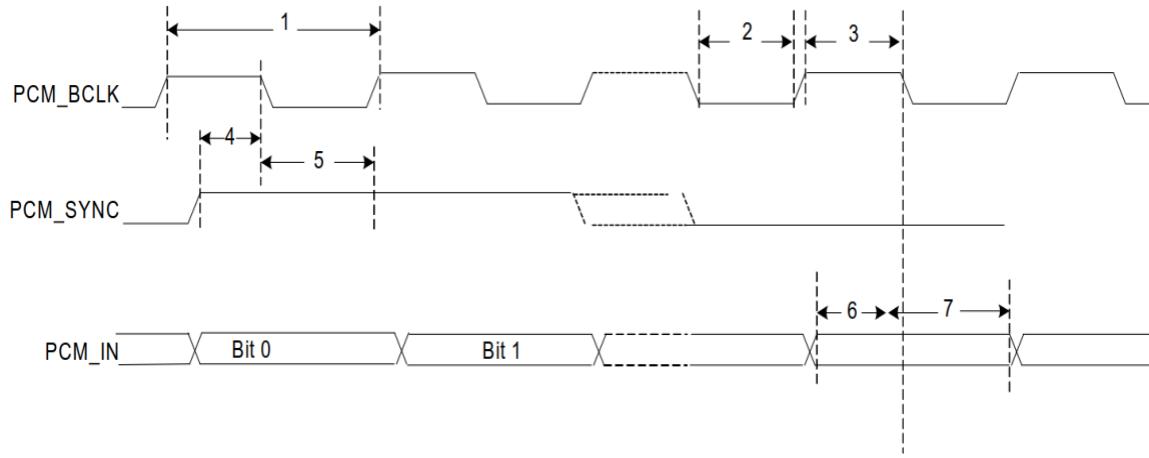

In long-frame synchronization mode, the frame synchronization signal is again an active-high pulse at the audio frame rate; however, the duration is three bit periods and the pulse starts coincident with the first bit of the first slot.

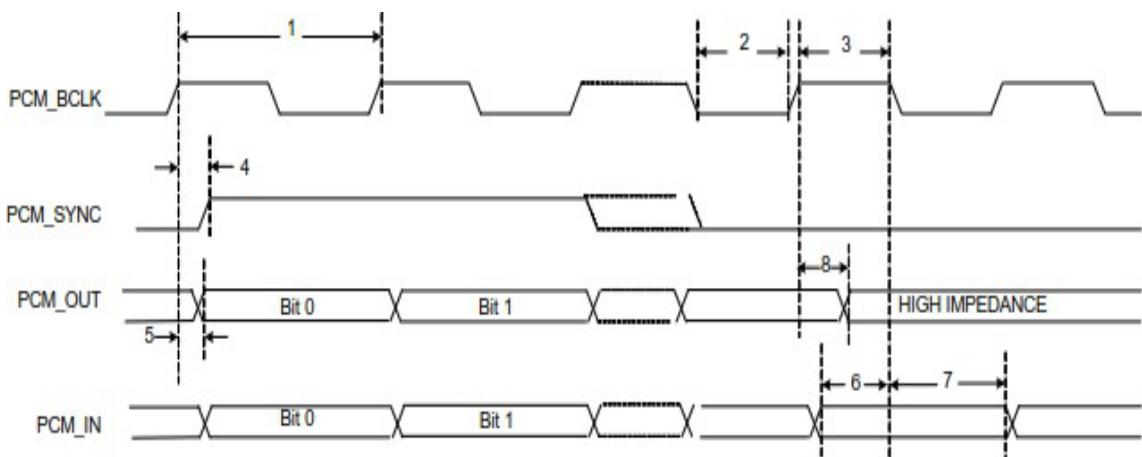

Figure 4 and Table 11 shows PCM Timing Diagram and Specifications for the master mode of long-frame.

Figure 4: PCM timing diagram (Long-Frame Sync, Master Mode)

Table 11: PCM Interface timing specifications (Long-Frame Sync, Master Mode)

| Ref No. | Characteristics                                                                              | Minimum | Typical | Maximum | Unit |

|---------|----------------------------------------------------------------------------------------------|---------|---------|---------|------|

| 1       | PCM bit clock frequency                                                                      | -       | -       | 12      | MHz  |

| 2       | PCM bit clock LOW                                                                            | 41      | -       | -       | ns   |

| 3       | PCM bit clock HIGH                                                                           | 41      | -       | -       | ns   |

| 4       | PCM_SYNC delay                                                                               | 0       | -       | 25      | ns   |

| 5       | PCM_OUT delay                                                                                | 0       | -       | 25      | ns   |

| 6       | PCM_IN setup                                                                                 | 8       | -       | -       | ns   |

| 7       | PCM_IN hold                                                                                  | 8       | -       | -       | ns   |

| 8       | Delay from rising edge of PCM_BCLK during last bit period to PCM_OUT becoming high impedance | 0       | -       | 25      | ns   |

Figure 5 and Table 12 shows PCM Timing Diagram and Specifications for the slave mode of long-frame.

Figure 5: PCM timing diagram (Long-Frame Sync, Slave Mode)

Table 12: PCM Interface timing specifications (Long-Frame Sync, Slave Mode)

| Ref No. | Characteristics                                                                              | Minimum | Typical | Maximum | Unit |

|---------|----------------------------------------------------------------------------------------------|---------|---------|---------|------|

| 1       | PCM bit clock frequency                                                                      | -       | -       | 12      | MHz  |

| 2       | PCM bit clock LOW                                                                            | 41      | -       | -       | ns   |

| 3       | PCM bit clock HIGH                                                                           | 41      | -       | -       | ns   |

| 4       | PCM_SYNC setup                                                                               | 8       | -       | -       | ns   |

| 5       | PCM_SYNC_hold                                                                                | 8       | -       | -       | ns   |

| 6       | PCM_OUT delay                                                                                | 0       | -       | 25      | ns   |

| 7       | PCM_IN setup                                                                                 | 8       | -       | -       | ns   |

| 8       | PCM_IN hold                                                                                  | 8       | -       | -       | ns   |

| 9       | Delay from rising edge of PCM_BCLK during last bit period to PCM_OUT becoming high impedance | 0       | -       | 25      | ns   |

### 7.3.3. Data Formatting

The 03ACCY0002 may be configured to generate and accept several different data formats. For conventional narrowband speech mode, the 03ACCY0002 uses 13 of the 16 bits in each PCM frame. The location and order of these 13 bits can be configured to support various data formats on the PCM interface. The remaining three bits

are ignored on the input and may be filled with 0s, 1s, a sign bit, or a programmed value on the output. The default format is 13-bit 2's complement data, left justified, and clocked MSB first.

#### 7.3.4. Wideband Speech Support

When the host encodes Wideband Speech (WBS) packets in transparent mode, the encoded packets are transferred over the PCM bus for an eSCO voice connection. In this mode, the PCM bus is typically configured in master mode for a 4-kHz sync rate with 16-bit samples, resulting in a 64 Kbps bit rate. The 03ACCY0002-Sx also supports slave transparent mode using a proprietary rate-matching scheme. In SBC-code mode, linear 16-bit data at 16 kHz (256 Kbps rate) is transferred over the PCM bus.

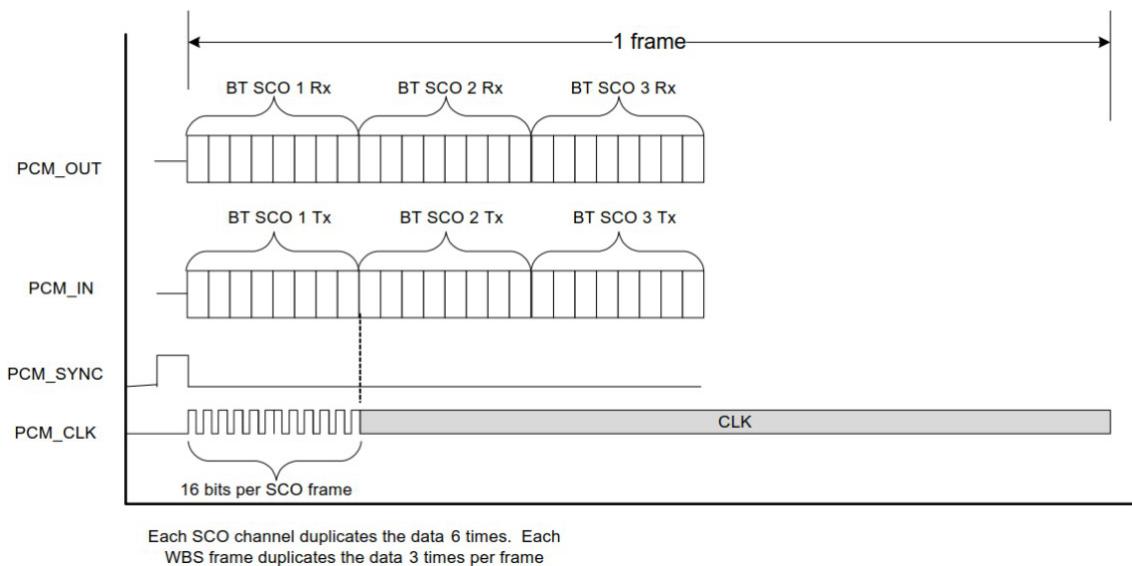

#### 7.3.5. Multiplexed Bluetooth Over PCM

Bluetooth supports multiple audio streams within the Bluetooth channel and both 16 kHz and 8 kHz streams can be multiplexed. This mode of operation is only supported when the Bluetooth host is the master. [Figure 6](#) shows the operation of the multiplexed transport with three simultaneous SCO connections. To accommodate additional SCO channels, the transport clock speed is increased. To change between modes of operation, the transport must be halted and restarted in the new configuration.

*Figure 6: Functional multiples data diagram*

#### 7.3.6. Burst PCM Mode

In this mode of operation, the PCM bus runs at a significantly higher rate of operation to allow the host to duty cycle its operation and save current. In this mode of operation, the PCM bus can operate at a rate of up to 24 MHz. This mode of operation is initiated with an HCI command from the host.

[Figure 7](#) and [Table 13](#) shows PCM Burst mode timing diagram and specifications for the receive-only mode of short-frame sync.

Figure 7: PCM burst mode timing (Receive Only, Short Frame Sync)

Table 13: PCM burst mode specifications (Receive Only, Short-Frame Sync)

| Ref No. | Characteristics         | Minimum | Typical | Maximum | Unit |

|---------|-------------------------|---------|---------|---------|------|

| 1       | PCM bit clock frequency | -       | -       | 24      | MHz  |

| 2       | PCM bit clock LOW       | 20.8    | -       | -       | ns   |

| 3       | PCM bit clock HIGH      | 20.8    | -       | -       | ns   |

| 4       | PCM_SYNC setup          | 8       | -       | -       | ns   |

| 5       | PCM_SYNC_hold           | 8       | -       | -       | ns   |

| 6       | PCM_IN setup            | 8       | -       | -       | ns   |

| 7       | PCM_IN hold             | 8       | -       | -       | ns   |

Figure 8 and Table 14 shows PCM Burst mode timing diagram and specifications for the receive-only mode of long-frame sync.

Figure 8: PCM burst mode timing (Receive Only, Long Frame Sync)

Table 14: PCM burst mode specifications (Receive Only, Long-Frame Sync)

| Ref No. | Characteristics         | Minimum | Typical | Maximum | Unit |

|---------|-------------------------|---------|---------|---------|------|

| 1       | PCM bit clock frequency | -       | -       | 24      | MHz  |

| 2       | PCM bit clock LOW       | 20.8    | -       | -       | ns   |

| Ref No. | Characteristics    | Minimum | Typical | Maximum | Unit |

|---------|--------------------|---------|---------|---------|------|

| 3       | PCM bit clock HIGH | 20.8    | -       | -       | ns   |

| 4       | PCM_SYNC setup     | 8       | -       | -       | ns   |

| 5       | PCM_SYNC_hold      | 8       | -       | -       | ns   |

| 6       | PCM_IN setup       | 8       | -       | -       | ns   |

| 7       | PCM_IN hold        | 8       | -       | -       | ns   |

## 7.4. I<sup>2</sup>S Interface

The 03ACCY0002-Sx supports two independent I<sup>2</sup>S digital audio ports. The I<sup>2</sup>S interface supports both master and slave modes. The I<sup>2</sup>S signals are:

- I<sup>2</sup>S clock: I<sup>2</sup>S SCK

- I<sup>2</sup>S Word Select: I<sup>2</sup>S WS

- I<sup>2</sup>S Data Out: I<sup>2</sup>S SDO

- I<sup>2</sup>S Data In: I<sup>2</sup>S SDI

I<sup>2</sup>S SCK and I<sup>2</sup>S WS become outputs in master mode and inputs in slave mode, while I<sup>2</sup>S SDO always stays as an output. The channel word length is 16 bits and the data is justified so that the MSB of the left-channel data is aligned with the MSB of the I<sup>2</sup>S bus, per the I<sup>2</sup>S specification. The MSB of each data word is transmitted one bit clock cycle after the I<sup>2</sup>S WS transition, synchronous with the falling edge of bit clock. Left-channel data is transmitted when I<sup>2</sup>S WS is low, and right-channel data is transmitted when I<sup>2</sup>S WS is high. Data bits sent by the 03ACCY0002 are synchronized with the falling edge of I<sup>2</sup>S\_SCK and should be sampled by the receiver on the rising edge of I<sup>2</sup>S\_SSCK.

The clock rate in master mode is either of the following:

$$48 \text{ kHz} \times 32 \text{ bits per frame} = 1.536 \text{ MHz}$$

$$48 \text{ kHz} \times 50 \text{ bits per frame} = 2.400 \text{ MHz}$$

The master clock is generated from the input reference clock using a N/M clock divider.

In the slave mode, any clock rate is supported to a maximum of 3.072 MHz.

### 7.4.1. I<sup>2</sup>S Timing

Timing values specified in Table 15 are relative to high and low threshold levels.

Table 15: Timing for I<sup>2</sup>S transmitters and receivers

|                                                                | Transmitter         |                     |                     |     | Receiver            |                     |             |     | Notes |  |

|----------------------------------------------------------------|---------------------|---------------------|---------------------|-----|---------------------|---------------------|-------------|-----|-------|--|

|                                                                | Lower Limit         |                     | Upper Limit         |     | Lower Limit         |                     | Upper Limit |     |       |  |

|                                                                | Min                 | Max                 | Min                 | Max | Min                 | Max                 | Min         | Max |       |  |

| Clock Period T                                                 | T <sub>tr</sub>     | -                   | -                   | -   | T <sub>r</sub>      | -                   | -           | -   |       |  |

| <b>Master Mode: Clock generated by transmitter or receiver</b> |                     |                     |                     |     |                     |                     |             |     |       |  |

| HIGH t <sub>HC</sub>                                           | 0.35T <sub>tr</sub> | -                   | -                   | -   | 0.35T <sub>tr</sub> | -                   | -           | -   |       |  |

| LOW t <sub>LC</sub>                                            | 0.35T <sub>tr</sub> | -                   | -                   | -   | 0.35T <sub>tr</sub> | -                   | -           | -   |       |  |

| <b>Master Mode: Clock generated by transmitter or receiver</b> |                     |                     |                     |     |                     |                     |             |     |       |  |

| HIGH t <sub>HC</sub>                                           | -                   | 0.35T <sub>tr</sub> | -                   | -   | -                   | 0.35T <sub>tr</sub> | -           | -   |       |  |

| LOW t <sub>LC</sub>                                            | -                   | 0.35T <sub>tr</sub> | -                   | -   | -                   | 0.35T <sub>tr</sub> | -           | -   |       |  |

| Rise time t <sub>RC</sub>                                      | -                   | -                   | 0.15T <sub>tr</sub> | -   | -                   | -                   | -           | -   |       |  |

|                     | Transmitter |   |   |      | Receiver |                   |   |   | Notes |

|---------------------|-------------|---|---|------|----------|-------------------|---|---|-------|

| <b>Transmitter</b>  |             |   |   |      |          |                   |   |   |       |

| Delay $t_{dtr}$     | -           | - | - | 0.8T | -        | -                 | - | - |       |

| Hold time $t_{htr}$ | 0           | - | - | -    | -        | -                 | - | - |       |

| <b>Receiver</b>     |             |   |   |      |          |                   |   |   |       |

| Setup time $t_{sr}$ | -           | - | - | -    | -        | 0.2T <sub>r</sub> | - | - |       |

| Hold time $t_{hr}$  | -           | - | - | -    | -        | 0                 | - | - |       |

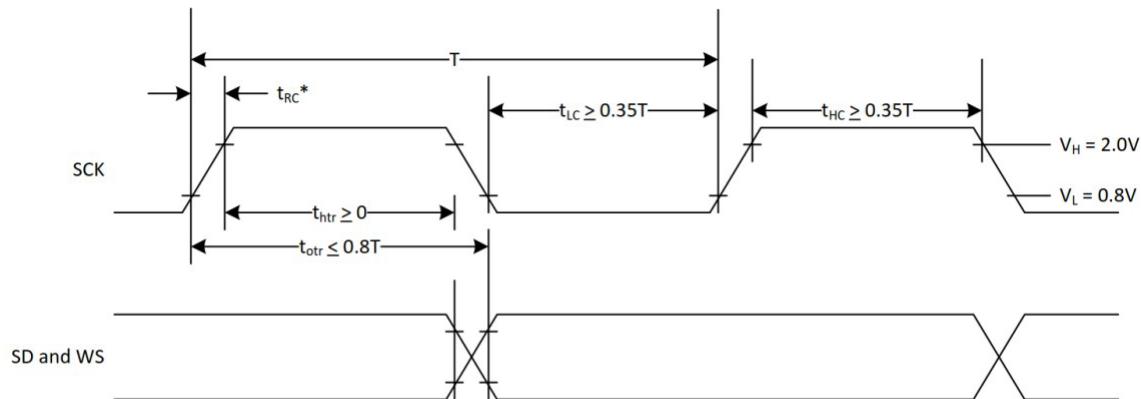

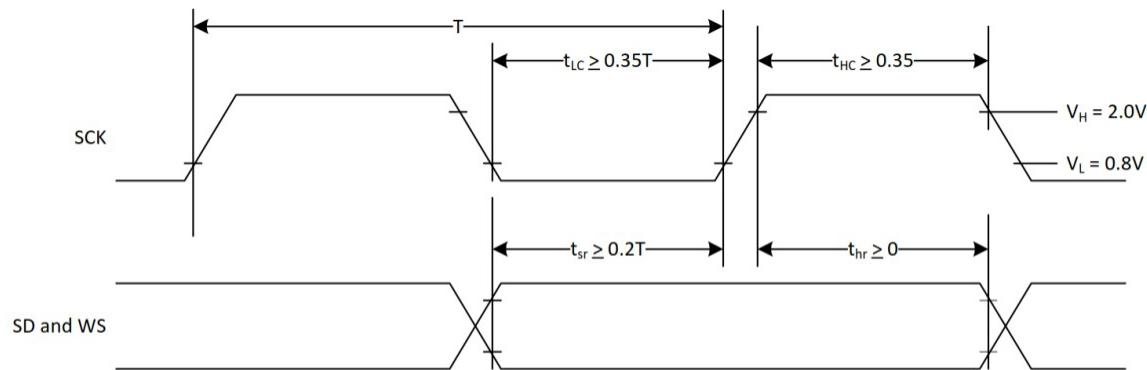

The time periods specified in [Figure 9](#) and [Figure 10](#) are defined by the transmitter speed. The receiver specifications must match transmitter performance.

$T$  = Clock period

$T_r$  = Minimum allowed clock period for transmitter

$T = T_r$

\*  $t_{RC}$  is only relevant for transmitters in slave mode.

**Figure 9: I2S transmitter timing**

$T$  = Clock period

$T_r$  = Minimum allowed clock period for transmitter

$T > T_r$

**Figure 10: I2S receiver timing**

## 8 FCC REGULATORY

| Model      | US/FCC (15.247) | CANADA/IC (RSS-247) |

|------------|-----------------|---------------------|

| 03ACCY0002 | 2A3FV-ECB02     | 28102-ECB02         |

The 03ACCY0002 has been designed to operate with the antenna listed below.

| Item    | Part Number    | Mfg.                  | Type         | Gain (dBi) |

|---------|----------------|-----------------------|--------------|------------|

| Antenna | 2450A T18D0100 | Johanson Technologies | Ceramic Chip | -2.7       |

### 8.1. Documentation Requirements

To ensure regulatory compliance, when integrating the 03ACCY0002 into a host device, it is necessary to meet the documentation requirements set forth by the applicable regulatory agencies. The following sections (FCC and Industry Canada) outline the information that may be included in the user's guide and external labels for the host devices into which the 03ACCY0002 is integrated.

**IMPORTANT:**

If the conditions above cannot be met (for example certain device configurations or co-location with another transmitter), then the FCC authorization is no longer considered valid and the FCC ID cannot be used on the final product. In these circumstances, the OEM integrator will be responsible for re-evaluating the end product (including the transmitter) and obtaining a separate FCC authorization.

When using Enovation Controls's FCC grant for the 03ACCY0002, the integrator must include specific information in the user's guide for the device into which the 03ACCY0002 is integrated. The integrator must not provide information to the end user regarding how to install or remove this RF module in the user's manual of the device into which the 03ACCY0002 is integrated. The following FCC statements must be added in their entirety and without modification into a prominent place in the user's guide for the device into which the 03ACCY0002 is integrated:

**This device is intended only for OEM integrators under the following conditions:**

This transmitter must not be co-located or operating in conjunction with any other antenna or transmitter, except in accordance with FCC multi-transmitter product procedures. The integrator is responsible for testing their end product for any additional compliance requirements required with this module installed. Reference FCC KDB 996369 D04 for details.

**End Product Labeling**

The final end product must be labeled in a visible area with the following:

***Contains FCC ID: 2A3FV-ECB02.***

**Manual Information to the End User**

The OEM integrator must be aware to not provide information to the end user regarding how to install or remove this RF module in the user's manual of the end product which integrates this module.

The end user manual shall include all required regulatory information/warning as show in this manual.

***Federal Communication Commission Interference Statement***

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

**FCC Caution:** Any changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate this equipment.

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

**IMPORTANT NOTE: FCC Radiation Exposure Statement:**

This equipment complies with the US portable RF exposure limit set forth for an uncontrolled environment and are safe for intended operation as described in this manual. The further RF exposure reduction can be achieved if the product can be kept as far as possible from the user body or set the device to lower output power if such function is available.

This transmitter must not be co-located or operating in conjunction with any other antenna or transmitter.

**FCC KDB 996369 D03 Summary**

| Section | Requirement                                                   | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2     | List of applicable FCC rules                                  | Title 47 Chapter I Subchapter C Part §15.247                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.3     | Summarize the specific operational use conditions             | Not applicable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.4     | Limited module procedures                                     | Not applicable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.5     | Trace antenna designs                                         | Not applicable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.6     | RF exposure considerations                                    | Portable exposure exclusion levels when used stand alone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.7     | Antennas                                                      | Integrated chip antenna                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.8     | Label and compliance information                              | Contains FCC ID: 2A3FV-ECB02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.9     | Information on test modes and additional testing requirements | <p>Host product manufacturers are responsible to follow the integration guidance and to perform a limited set of transmitter module verification testing, to ensure the end product is in compliance with the FCC rules.</p> <p>Also host product manufacturers are responsible for all additional equipment authorization and testing for technical requirements not covered by the module grant (e.g., unintentional radiator Part 15 Subpart B requirements, or transmitters used in the host that are not certified modules).</p> <p>Device programmed using CyBluetool ver 0.1.97.1. Bluetooth Classic using Basic Rate and Enhanced Data Rate on channels 0 (2402 MHz), 39 (2440 MHz), 78 (2480 MHz), and Hopping.</p> |

| 2.10    | Additional testing, Part 15 Subpart B disclaimer              | The final host product requires Part 15 Subpart B compliance testing with the modular transmitter installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## **Innovation Economic Development Canada**

This device complies with Industry Canada's license-exempt RSSs. Operation is subject to the following two conditions:

1. This device may not cause interference; and

2. This device must accept any interference, including interference that may cause undesired operation of the device.

Le présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio exempts de licence. L'exploitation est autorisée aux deux conditions suivantes:

1. l'appareil ne doit pas produire de brouillage;

2. l'utilisateur de l'appareil doit accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

### **Radiation Exposure Statement:**

The product complies with the Canada portable RF exposure limit set forth for an uncontrolled environment and are safe for intended operation as described in this manual. The minimum separation distance for portable use is limited to 15mm. The further RF exposure reduction can be achieved if the product can be kept as far as possible from the user body or set the device to lower output power if such function is available.

### **Déclaration d'exposition aux radiations:**

Le produit est conforme aux limites d'exposition pour les appareils portables RF pour les Etats-Unis et le Canada établies pour un environnement non contrôlé. Le produit est sûr pour un fonctionnement tel que décrit dans ce manuel. La réduction aux expositions RF peut être augmentée si l'appareil peut être conservé aussi loin que possible du corps de l'utilisateur ou que le dispositif est réglé sur la puissance de sortie la plus faible si une telle fonction est disponible.

This device is intended only for OEM integrators under the following conditions:

- The transmitter module may not be co-located with any other transmitter or antenna.

The integrator is responsible for testing their end-product for any additional compliance requirements required with this module installed.

Cet appareil est conçu uniquement pour les intégrateurs OEM dans les conditions suivantes:

- Le module émetteur peut ne pas être coïmplanté avec un autre émetteur ou antenne.

Tant que les 1 condition ci-dessus sont remplies, des essais supplémentaires sur l'émetteur ne seront pas nécessaires. Toutefois, l'intégrateur OEM est toujours responsable des essais sur son produit final pour toutes exigences de conformité supplémentaires requis pour ce module installé.

**IMPORTANT NOTE:**

If these conditions cannot be met (for example, certain laptop configurations or co-location with another transmitter), then the Canada authorization is no longer considered valid and the IC ID cannot be used on the final product. In these circumstances, the OEM integrator will be responsible for re-evaluating the end product (including the transmitter) and obtaining a separate Canada authorization.

**NOTE IMPORTANTE:**

Dans le cas où ces conditions ne peuvent être satisfaites (par exemple pour certaines configurations d'ordinateur **portable** ou de certaines co-localisation avec un autre émetteur), l'autorisation du Canada n'est plus considéré comme valide et l'ID IC ne peut pas être utilisé sur le produit final. Dans ces circonstances, l'intégrateur OEM sera chargé de réévaluer le produit final (y compris l'émetteur) et l'obtention d'une autorisation distincte au Canada.

**End Product Labeling**

The final end product must be labeled in a visible area with the following: "Contains IC: 28102-ECB02".

**Plaque signalétique du produit final**

Le produit final doit être étiqueté dans un endroit visible avec l'inscription suivante:

"Contient des IC: 28102-ECB02".

**Manual Information to the End User**

The OEM integrator must be aware not to provide information to the end user regarding how to install or remove this RF module in the user's manual of the end product which integrates this module.

The end user manual shall include all required regulatory information/warning as show in this manual.

**Manuel d'information à l'utilisateur final**

L'intégrateur OEM doit être conscient de ne pas fournir des informations à l'utilisateur final quant à la façon d'installer ou de supprimer ce module RF dans le manuel de l'utilisateur du produit final qui intègre ce module. Le manuel de l'utilisateur final doit inclure toutes les informations réglementaires requises et avertissements comme indiqué dans ce manuel.

This radio transmitter (*IC: 28102-ECB02*) has been approved by *Industry Canada* to operate with the antenna types listed below with the maximum permissible gain indicated. Antenna types not included in this list, having a gain greater than the maximum gain indicated for that type, are strictly prohibited for use with this device.

Le présent émetteur radio (*IC: 28102-ECB02*) a été approuvé par Industrie Canada pour fonctionner avec les types d'antenne énumérés ci-dessous et ayant un gain admissible maximal. Les types d'antenne non inclus dans cette liste, et dont le gain est supérieur au gain maximal indiqué, sont strictement interdits pour l'exploitation de l'émetteur.

| Item    | Part Number    | Mfg.                  | Type         | Gain (dBi) |

|---------|----------------|-----------------------|--------------|------------|

| Antenna | 2450A T18D0100 | Johanson Technologies | Ceramic Chip | -2.7       |

## 13 ADDITIONAL ASSISTANCE

Please contact your local sales representative or our support team for further assistance:

Enovation Controls

Support: <https://support.enovationcontrols.com/hc/en-us>

Email: [support@enovationcontrols.com](mailto:support@enovationcontrols.com)

Phone: +1.918.317.4100

Web: <https://www.enovationcontrols.com>