## Exhibit 2 Equipment Description

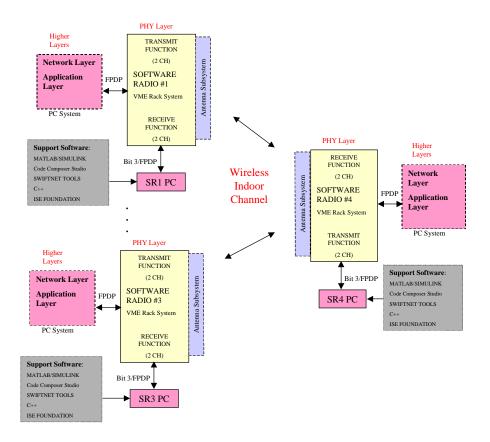

The configuration of the Georgia Tech Software Radio Laboratory for the proposed experimental set-up is illustrated in Figure 2.1. The relevant systems in the lab associated with this application include software radio platforms, associated antenna subsystems, software radio host/control PCs, and MAC application layer host PCs.

Figure 2.1. Software Radio Laboratory Configuration

Table 2.1 provides a list of the key components comprising the wireless radios for which the license application is being made.

| Sub System                   | Component                                  | Manufacturer                               | Model Numbers                                                             | Comments                                                                                                                                    |

|------------------------------|--------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| RF RX                        | Two-channel RF to baseband converter       | APCOM                                      | 1610 RB28 and<br>1610 RBC40<br>(upgrade)                                  | Receive-only 28 MHz and 40 MHz (upgrade)                                                                                                    |

|                              | Synthesizer for<br>Receive Channels        | APCOM                                      | 1610-SYN-140C                                                             | Provides tunable LO for RF downconverters                                                                                                   |

| RF Tx                        | Two-channel<br>baseband to RF<br>converter | APCOM                                      | 1610 BRC40                                                                | Transmit only; 40 MHz max<br>BW                                                                                                             |

| (Option 1)                   | Synthesizer for<br>Transmit Channels       | APCOM                                      | 1610 SYN-140C                                                             | Provides tunable LO for IF to<br>RF upconversion                                                                                            |

| RF Tx<br>(Option 2)          | Signal Generators                          | Agilent                                    | Model 4433B ESG-<br>D<br>Model E4438C                                     | IF to RF upconversion (<20<br>MHz)<br>IF to RF upconversion (>20                                                                            |

| Antenna<br>(Configuration 1) | Straight 3 dBi stub<br>Antenna             | unknown                                    | (upgrade)<br>unknown                                                      | MHz)<br>Handset antenna                                                                                                                     |

| Antenna<br>(Configuration 2) | Beam-switched<br>antenna array             | Custom GT<br>design (See<br>exhibit 4)     | N/A                                                                       | Provides beam selection<br>capability                                                                                                       |

| IF Rx                        | Wideband Digital<br>Receiver               | Pentek                                     | Model 1616 (26<br>MHz max BW) and<br>Model 6235 (50MHz<br>max BW) upgrade | Provides A/D conversion and<br>digital downconversion to<br>complex baseband; The<br>model 6235 has an embedde<br>FPGA                      |

| IF/ Baseband<br>Processing   | Quad Processor<br>boards                   | Pentek                                     | Models 4291, and 4291-330, and 4294                                       | Quad processing boards<br>based on the TI C6701 and<br>also Motorola's Altivec G4<br>Power PC processors; For II<br>and Baseband processing |

|                              | FPGA boards                                | Pentek                                     | Model 6250                                                                |                                                                                                                                             |

| IF Tx                        | D/A Conversion<br>boards                   | Pentek                                     | Model 6229                                                                | Digital to analog conversior<br>and I/Q upconversion to IF<br>frequency; Max BW per<br>DAC channel is 12.5 MHz                              |

| I/O                          | VME-based FPDP<br>I/O boards               | Pentek                                     | Model 6226                                                                | FPDP I/O channel (via<br>parallel cable) from softwar<br>radio to application PC                                                            |

|                              | PC-based FPDP I/O<br>boards                | VMETRO                                     | DPIO                                                                      | Provides FPDP I/O link to<br>the PCI bus in the applicatio<br>PC                                                                            |

|                              | PCI-to-VME I/O<br>boards                   | Pentek                                     | Model 4229                                                                | VME-to-PCI interface data<br>link with host PC                                                                                              |

|                              | Raceway<br>Interconnect boards             | Pentek                                     | Model 6219                                                                | Provides high-rate data path<br>across multiple quad DSP<br>boards                                                                          |

| Data Collection              | 1GB and 2 GB buffer                        | Communication<br>Automation<br>Corporation | 6VDL2A                                                                    | High data rate buffers                                                                                                                      |

| Computers                    | Host Computers                             | Dell Computers                             | Dell WorkStations                                                         | Host development tools and<br>control/programming of<br>software radio                                                                      |

Table 2.1

Key Components (including anticipated future components) Comprising the Experimental Wireless Radios

| Application PCs | Dell      | Dell WorkStations | Hosts the MAC and other     |

|-----------------|-----------|-------------------|-----------------------------|

|                 | Computers |                   | higher layers in the system |

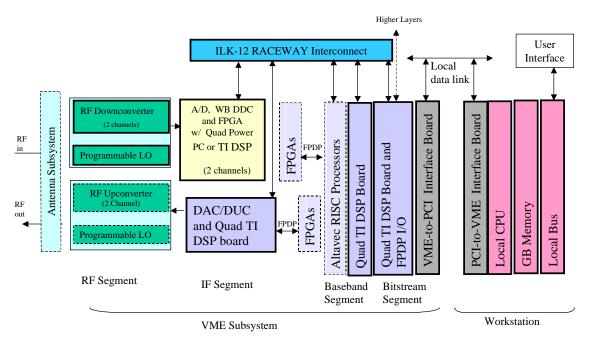

As shown in Figure 2.2, the GT software radio is configured for both receive and transmit processing functions. Each software radio is implemented as a VME rack system populated with COTS equipment to provide functions associated with RF down- and up-conversion, analog-to-digital conversion, digital-to-analog conversion, IF processing, baseband processing, and bitstream processing. A high data rate bus, called RACEWAY, is shared between processing boards to facilitate data transfers at rates up to 160 Mb/s. Each software radio is to be connected via an FPDP I/O link to a dedicated PC for the MAC and/or application layers associated with the modem. A photo of a software radio platform is shown in Figure 2.3.

\*Note: Design based partly on architecture proposed by Joe Mitola

## Figure 2.2. Software Radio Platform Configuration

Receive Chain

The receive RF front-end in each software radio platform includes a synthesizer board and two downconversion channels. These RF boards, obtained from APCOM Inc., include capability to synchronously downconvert input RF frequencies up to 3 GHz. The synthesizer board generates a programmable LO signal that is shared by the downconversion boards for synchronous operation. The down-conversion boards each represent a separate physical receive channel with down-conversion circuitry, including image rejection filters, low noise amplifiers (LNAs), filters, amplifiers, and mixers. RF signals may be input to the receiver boards via cable connections from the outputs of the RF channel emulators or other sources. The input signals are filtered in the receiver to a spectral footprint of 28 MHz (40 MHz upgrade is pending), and are then down-converted to a low IF frequency for analog to digital conversion. The selection of the IF is driven by the A/D sampling rate associated with the A/D converters in the digital receiver boards that follow the RF down-conversion boards. C-based programs were developed to control the boards from the software radio (SR) host computers.

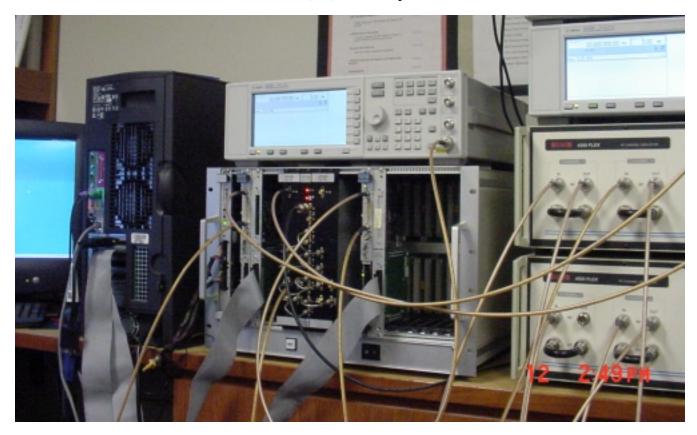

**Figure 2.3**. Photo of the Software Radio Platform with a VME/PCI controller, a twochannel Wideband Receiver Module and a dual FPDP module mounted on a Quad TI C6701 DSP board, two phase-coherent RF downconversion channels with a shared synthesizer board, and a DAC/DUC board and dual FPDP board mounted on a Quad TI C6701 DSP board. The signal generator is used for IF to RF conversion.

The resulting IF signals are applied to the inputs of the digital receiver boards, where the signals are prefiltered with anti-aliasing filters and are sampled with A/D converters at a rates up to 105 Msamples/s. Signal bandwidths in excess of the desired 40 MHz signal bandwidth can be sampled without aliasing. Following the sampling operation, the signals are converted to complex baseband with digital receiver chips. The wideband down-converters support output bandwidths up to 40 MHz. The digital receiver chips have numerically controlled oscillators (NCOs), filters, and decimators for the down-

conversion process. Synchronous demodulation across as many as eight channels is possible. If intermediate frequency (IF) processing is desired, such as for despreading or digital downconversion, the digital down-converters can be bypassed and the sampled signals output directly to an FPGA (on –board) or to a Pentek quad processing board.

Following down-conversion to baseband, the sampled signals are buffered to a quad DSP boards for baseband and bitstream processing, which could include baseband demodulation, decoding, and other processing functions. A RACEWAY interconnect is available to support high data-rate transfers between quad processor boards. The anticipated configuration will include four quad DSP boards and two quad Power PC boards all connected to a RACEWAY crossbar switch. An FPGA board will be acquired to support FPGA-based baseband processing. Following signal processing, the demodulated data is passed through an FPDP I/O link to a dedicated host platform for higher layer functions, or alternatively to a large (i.e., 2 Gbyte) memory buffer via FPDP for signal storage and post collection processing.

## Transmit Chain

The transmit chain is projected to include data framing, data transfer from the application PC to the software radio platform, interleaving, FEC coding, space-time coding, symbol formation, OFDM modulation, guard insertion, digital to analog conversion, and IF-to-RF frequency conversion. Data from the application PC is streamed to a quad processing board in the software radio via an FPDP I/O link. Baseband modulation processing can be accomplished with the processing board and optionally with support from an FPGA board. The resulting baseband real and complex samples are buffered to a DAC/DUC, which performs digital to analog conversion, I/Q modulation, and upconversion to IF. The resulting analog IF signal is input to an IF to RF converter. A signal generator or dedicated VME-based transmit boards will be utilized for this function for the frequency conversion and transmit functions. The RF transmit front end is to provide 2-channel operation.

The specific operating characteristics of the prototype radios for the proposed experimental license are indicated in Exhibit 3. Note that the experimental set-up includes single and multiple antenna configurations with straight 3 dBi antenna elements and a multiple antenna configuration with higher-gain beams derived from the Georgia Tech beamswitch antenna array.